Дешифратор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 435587

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Рестгубпик (61) Зависимое от авт. свидетельства (22) Заявлено 06.09.71 (21) 1693304/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 05.07.74. Бюллетень № 25 (51) М. Кл. H 03k 13/00

Государственный комитет

Совета Министров СССР аа делам изаоретеиий и открытий (53) УДК 621.394.625. .33 (088.8) Дата опубликования описания 21.11.74 (72) Авторы изобретения

В. В. Федоровский и Д. М. Компанец

Институт автоматики (71) Заявитель щ p fgf. É 11 . «т j g g (54) ДЕ 1Ц И Ф РАТО Р

Изобретение относится к автоматике, может быть .использовано на приемном конце телемеханического канала, в частности в системах радиоуправления стрелочными переводами из кабины локомотива.

Дешифраторы, содержащи е узел взаимно сбло кированных воспринимающих элементов, выходы которых соединены со,входами соответст вующ их фиксирующих элементов запоминающего узла, выход которого совместно с другими выходами каж дого воспринимающего элемента включены в схему коммутации выходных цепей, уже известны.

Цель изобретения — упрощение схемы, повышение надежности и устойчивости к импульсным помехам — достигается тем, что в предлагаемый дешифратор введены элементы регулируемой задержки, буферный запоминающий элемент с регулировкой длительности запоминания и буферный блокировочный элемент, .причем один из входоB каждого воспринманиющего элемента,по схеме «ИЛИ» соединен со входом элемента регулируемой задержки и с целью само блокировки буферного блокировочного элемента, вход которого по схеме «И» соединен с инверсным выходом элемента регулируемой задержки и одним из прямых выходов буферного запоминающего элемента, вход которого по схеме «И» соединен с одним из прямых выходов элемента регулируемой задержки и инверсным выходом буферного блокировочного элемента; второй прямой, выход элемента регулируемой задержки соединен со

5 схемой коммутации выходных цепей, а прямые выходы обоих буферных элементов по схеме «ИЛИ» соединены с общим входом запоминающего узла.

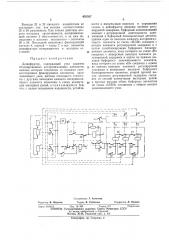

На чертеже приведена схема предлагаемого

10 устройства.

Дешифратор содержит взаимно сблокированные воспринимающие элементы 1 — 3, фиксирующие элементы 4 — 6 запоминающего узла и схему коммутации выходных цепей 7.

15 Выходы 8 — 10 воспринимающих элементов

1 — 3 соединены со входами соответствующих фиксирующих элементов 4 — 6 запоминающего узла, выходы 11 — 13 которых совместно с другими выходами 14 — 16 каждого восприни20 мающего элемента включены в схему коммутации выходных цепей 7. На выходах 17 — 19 воспринимающих элементов включен элемент регулируемой задержки импульсов 20, на выходе 21 которого включен буферный запоми25 нающий элемент 22 с регулировочным устройством длительности запоминания, обеспечивающим запоминание первого импульса сигнала до поступления второго импульса. На выходе 23 элемента задержки включен буфер30 ный блокировочный элемент 24 с цепью само435587

3 блокировки для обеспечения подпитки одного из фиксирующих элементов 4 — 6 на период при ема второго импульса, а также для бези нерционного сброса этого элемента в конце приема сигнала. Третий выход 25 элемента задержки включен в схему коммутации выходных цепей 7 для выдачи сообщения на,выходе дешифратора только после контроля длительности второго импульса.

Фиксирующие элементы 4 — 6 запоминающего узла взаимно сблокированы собственными инверстными выходами 26 — 30, что исключает срабатывание какого-либо из этих элементов в период приема второго импульса сигнала и тем самым обеспечивает работу заявленного дешифратора при многократном использовании в нем воспринимающих элементов в период дешифрации сообщения. Прямые выходы 31, 32 обоих буферных элементов

22, 24 соединены с общим входом запоминающего узла.

Один из выходов 17 — 19 каждого воспринимающего элемента 1 — 3 по схеме «ИЛИ» соединен со входом элемента регулируемой задерж ки 20 и с цепью самоблокировки 33 буферного блокировочного элемента 24, вход которого по схеме «И» соединен с инверсным выходом 23 элемента регулируемой задержки

20 и одним из прямых выходов 34 буферного запоминающего элемента 22. Вход, последнего по схеме «И» соединен с одним из прямых выходов 21 элемента регулируемой задержки 20 ,и инверсным выходом 35 буферного блокировочного элемента 24.

Кроме того, для расширения области использования предлагаемого дешифратора путем применения его в телемеханических каналах с различыми в ремаными ха ракте р истиками KBK импульсов сигнала, так и интервалов между ними, в качестве задержки применены элемент регулируемой задержки и буферный запоминающий элемент с регулировочным устройством длительности запоминания.

Дешифратор работает следующим образом.

Первый частотный импульс кодированного сигнала воспринимается соответствующим элементом, например 1. В результате этого остальные воспринимающие элементы блокируются блокировочной связью, что исключает влияние импульсных помех через эти каналы на элемент 1 и в общем на .процесс дешифрации.

Сработав, элемент 1 выходом 8 подготавливает цепь для фиксирующего элемента 4, выходом 14 замыкает соответствующую цепь в схеме коммутации, выходных цепей 7, которая только в сочетании с выходами фиксирующих элементов других номеров, а не одноименных с номером воспринимающего элемента, обеспечивает выход (следовательно, в данном случае коммутация выхода 14 не имеет значения), а выходом .17 обеспечивает срабатывание элемента задержки 20 по истечении времени, установленного настройкой задерж5

4 ки (несколько меньшего длительности импульса).

В результате элемент задержки 20 .выходом

21 включает буферный запоминающий элемент 22, выходом 23 исключает возможность включения буферного блокировочного элемента 24 при срабатывании буферного запоминающего элемента 22, а выходом 25 включает схему коммутации выходных цепей 7, что, как указано выше, при приеме первого импульса не имеет значения. Буферный запоминающий элемент 2 выходом 31 через выход 8 элемента 11 включает фиксирующий элемент 4, который своим выходом 11 в схеме 7 замыкает определенную цепь. После окончания приема первого импульса элемент 22 выходом 31 удерживает этот фиксирующий элемент включенным через его собственный выход 28 в течение определенного промежутка времени, чем и обеспечивается запоминание первого импульса. С другой стороны, когда в конце приема первого импульса обесточивается элемент задержки 20, он своим инверсным выходом 23 через выход 34 элемента 22 включает буферный блокировочный элемент 24, который включает, цепь самоблокировки 33. В этом состоянии оба буферных и один фиксирующий элемент находятся в течение периода запоминания буферного запоминающего элемента, отрегулированного для приема телемеханического сигнала с определенной паузой между импульсами.

Если после истечения периода буферного запоминания второй импульс не поступает на вход узла воспринимающих элементов, все элементы дешифратора принимают исходное состояние. При восприятии второго импульса кодированного сигнала до момента окончания периода буферного запоминания, например, элементом 2, он блокирует остальные элементы, а его выходом,15 в сочетании с выходом 11 элемента 4 в схеме 7 подготавливается определенная выходная цепь данного дешифрированного сообщения; выход 9 никак не воздействует, так как инверсный выход 28 фиксирующего элемента 4 блокирует элементы 5, 6. Выход 18 с одной стороны обеспечивает самоблокировку буферного блокировочного элемента 24, а тем самым через его,выход 32,и запоминание первого импульса фиксирующим элементом 4, так как регулировкой периода буферного запоминания предусмотрено, чтобы в начале приема второго импульса этот период истек и буферный запоминающий элемент обесточился. С другой стороны обеспечивается срабатывание элемента задержки

20, который по истечении отрегулированного настройкой периода времени, если длительность импульса превышает этот период, срабатывает. В результате выход 25 включает схему коммутации выходных цепей 7, на выходе которой с этого момента до конца приема второго .импульса образуется подготовленная ранее сочетанием выходов 11 и 15 выходная цепь дешифрованного сообщения, 435587

Предмет изобретения

1 1

1 1

Составитель Г. Антонова

Техред В. Рыбалова

Корректор Л. Орлова

Редактор Б. Фе1ввтов

Заказ 3164/12 Изд. № 983 Тираж 811 Подписное

Ш-1ИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

Москва, %-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2,Выходы 21 и 23 никакого воздействия не оказывают, так как выходы соответственно

35 и 34 разомкнуты. Как только действие второго импульса заканчивается, воспринимаю,щий элемент 2 обесточивается, а за ним немедленно и,взаимно независимо — элементы

20 и 24. Последний выключает фиксирующий элемент 4, первый — схему 7, и все элементы дешифратора возвращаются в исходное состояние.

Дешифратор, содержащий узел взаимно сблокированных воспринимающих элементов, выходы которых соединены со входами соответствующих фиксирующих элементов запоминающего узла, выходы последнего совместно с другими выходами .каждого воспринимающего элемента включены в схему коммутации выходных цепей, отличающийся тем, что, с целью повышения надежности, устойчивости к импульсным помехам и упрощения схемы, в дешифратор введены элемент регулируемой задержки, буферный запоминающий элемент с регулировкой длительности запоминания и буферный блокировочный элемент, причем один из выходов каждо го.воспринимающего элемента по схеме «ИЛИ» соединен с входом элемента регулируемой задержки и с цепью самоблокировкии буферного блокиро1р вочного элемента, вход которого по схеме «И» соединен с инверсным выходом элемента регулируемой задержки и одним из прямых выходов буферного запоминающего элемента, вход которого по схеме «И» соединен с одним

15 из прямых выходов элемента регулируемой задержки и инверсным выходом буферного блокировочного элемента, второй прямой выход элемента регулируемой задержки соединен со схемой коммутации выходных цепей, а прямые выходы обоих буферных элементов по схеме «ИЛИ» соединены с общим входом запоминающего узла.