Побайтный преобразователь из двоичного в двоично- кодированное остаточное представление

Иллюстрации

Показать всеРеферат

ввсасоюандт

%an, !! -1 -: - q библиотека 1. БА (»> 437067

О ТИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Респубпин (61) Зависимое от авт. свидетельства (22) Заявлено 24.04.72 (21) 1779694/18-24 е присоединением заявки № (32) Приоритет

Опубликовано 25.07.74. Бюллетень № 27

Дата опубликования описания 15.1.75 (51) М. Кл. G 06f 5/02

Гасударст венный комитет

Совета Министров СССР во делам изобретений и открытий (53) УДК 681.325(088.8) (72) Автор изобретения

Н. А. Долинская (71) Заявитель (54) ПОБАЙТНЫЙ ПРЕОБРАЗОВАТЕЛЪ ИЗ ДВОИЧНОГО

В ДВОИЧНО-КОДИРОВАННОЕ ОСТАТОЧНОЕ ПРЕДСТАВЛЕНИЕ

16, 21, 1,6 11;

10, 22, 16, 19, 4;

20, 6, 28, 9, 13;

16, 1, 8, 2, 16. для mod 25 : 1, 6, 11, 20 для mod 27: 1, 13, 7, для mod 29: 1, 24, 25, для mod 31: 1, 8, 2, Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных машин и устройств, функционирующих в системе остаточных классов (СОК).

Известные преобразователи из двоичного в двоично-кодированное остаточное представление, основанные на помодульном суммировании поразрядных остаточных представлений с помощью каскадного соединения групп одноразрядных сумматоров, требуют для хранения остаточных представлений массивных запоминающих устройств и их р-тактного сложения по модулям, где р — число двоичных разрядов.

Цель изобретения — упрощение преобразователя и повышение его быстродействия.

Это достигается тем, что выходы дешифратора, соответствующие трем младшим разрядам байта, соединены с первыми входами всех табличных схем сложения, выходы дешифратора, соответствующие четырем старшим разрядам байта, соединены через первую группу диодных сборок со вторыми входами, а через вторую группу диодных сборок — с третьими входами соответствующих табличных схем сложения, а шина четвертого, младшего, разряда байта соединена с третьими ключевыми входами всех табличных схем сложения.

В предлагаемом преобразователе используется помодульное суммирование остаточных представлений, соответствующих целым байтам, а не отдельным двоичным разрядам в вычислительном устройстве или АУ ЭВМ, функционирующих в СОК, причем остаточное побайтное представление корректируется умножением на величину, постоянную для каждого байта:

Illð 12 1, 12" 1р 12" 1р f2" 1р

2 !24 ((2 @! (т;4-ый модуль СОК).

Для конкретного машинного множества взаимно простых модулей 25, 27, 29, 31, 32 эти величины соответствуют:

25 Побайтные преобразования по mod 32 выполняются с помощью только логических операций. Собственно однотактное побайтное преобразование реализуется с помощью обьединения модифицированных табличных схем

30 остаточного сложения, где в качестве вход437067 ных операндов фигурируют остаточные представления соответственно четырех младших и четырех старших разрядов байта.

Таким образом, используя модифицированные табличные схемы остаточного сложения в побайтном преобразователе совместно с одноактными табличными схемами остаточного сложения и умножения в АУ ЭВМ в СОК, быстродействие операции преобразования увеличивается почти втрое.

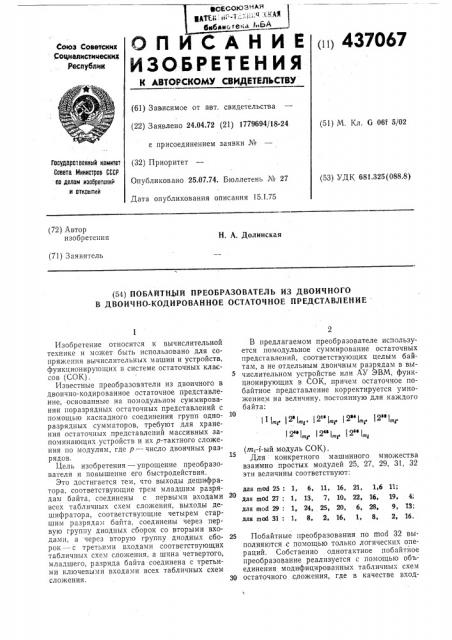

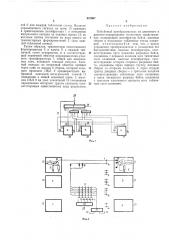

На фиг. 1 представлена функциональная схема предлагаемого побайтного преобразователя из двоичного в двоично-кодированное остаточное представление; на фиг. 2— функциональная схема поиска в группе неравнозначных мест с последующим декодированием; на фиг. 3 †табли сложения по модулю 29 для побайтного преобразователя, при этом на фиг. 3a — исходная та блица; на фиг.

Зб — модифицированная таблица.

Побайтный преобразователь содержит дешифратор 1, две группы диодных сборок 2 и

3, модульные табличные схемы 4 остаточного сложения, которые, в свою очередь, состоят из транзисторных формирователей 5, транзисторных ключей 6, координатно-узловых трансформаторов 7, импульсных диодов 8, пассивной кодовой линейки (ПКЛ) 9, усилителей 10 считывания, интегральных ключевых схем 11, входы 12 которых подключены к четвертому разряду байта. Выходы дешифратора 1, соответствующие первым трем младших разрядов байта, являются общими для всех табличных схем 4 остаточного сложения и подключены ко входам 13 транзисторных формирователей

5. Выходы первой группы диодных сборок 2 подключены ко входам 14 интегральных ключевых схем 11, а выходы второй группы диодных сборок 3 — ко входам 15 транзисторных ключей соответствующих табличных схем сложения побайтного преобразователя. Эмиттерные выходы 16 транзисторных формирователей 5 и коллекторные выходы 17 транзисторных ключей 6 соединены друг с другом через первичные обмотки координатно-узловых трансформаторов 7, определяющих только неравнозначные узловые места в базовых квадратах таблицы, и через импульсные диоды 18 интегральных сборок. Вторичные обмотки — координатно-узловых трансформаторов через импульсные диоды 8 интегральных сборок связаны с началом кодовых проводов расшифровки мест в ПКЛ 9, концы которых через интегральные ключевые схемы 11 подключены к общей земляной шине.

Цепь 19 служит для подачи управляющего сигнала (— ) на вход дешифратора 1, Ко входам 20 подаются на вход преобразователя восемь разрядов байта; шины 21 являются выходами преобразователя, которые связаны с входными регистрами сумматоров АУ в СОК (на фиг. 1 л 2 не показаны).

Результаты побайтного преобразования по модулю можно задать в виде таблицы остаточного сложения, где в качестве входных

1О

15 го

25 зо

S0

65 операндов взяты остаточные представления значений четырех младших 10 —:15 „, и четырех старших разрядов )16(0 —:15) ),, байта (см. фиг. 3a) . Упорядочивая расположение значений входного операнда, как показано на фиг. Зб, т. е. производя перекодировку на выходе дешифратора для этого операнда, приходим к модифицированной таблице остаточного сложения, где, как и в полной таблице сложения, равнозначные значения узлов расположены параллельно побочной диагонали.

Для каждого модуля аппаратурно реализуется табличная схема, «свернутая» до величины базового квадрата с учетом диагональной симметрии и микроструктурных свойств арифметических таблиц: однозначности взаимного отображения значений суммы между сходно расположенными квадратными табличными конфигурациями, начиная с базового квадрата со стороной 2 значения операндов и более, и незначительности объема неравнозначных значений суммы в пределах указанных квадратных конфигураций (фиг. Зб).

Для т;2 оптимальная сторона базового квадрата 2З и максимальное число неравнозначных мест сводится к 2 — 1; при этом схемно реализуются только до 75 узлов таблицы, так как в ней содержатся только 5 нетождественных базовых квадратов вместо 256 узлов полной таблицы.

Поскольку остаточное представление для младших разрядов байта на входе 20 преобразователя одинаково для всех модулей (младший модуль т;, равный 25, больше 15), то «свертка» в десятичные номера строк (столбцов) базового табличного квадрата выполняется дешифратором 1 по кодовым шинам

13, а «свертка» в кодовые шины номеров групп базовых квадратов — непосредственно по шинам 12 четвертого разряда байта, одновременно для всех табличных схем 4 остаточного сложения. «Свертка» в десятичные номера столбцов (строк базового квадрата) и в кодовые шины номеров групп базовых квадратов для операнда, представленного четырьмя старшими разрядами байта, выполняется одновременно для всех табличных схем дешифратором 1 совместно с группами диодных сборок 3, 2 соответственно.

Преобразователь работает следующим образом.

Наличие восьми разрядного двоичного кода на шинах 20 приводит к срабатыванию дешифратора 1 и появлению рабочего потенциала на выходах групп диодных сборок 2, 3, на одной из шин 14, 15, а также на одной из шин

12 для каждой табличной схемы. Наличие потенциалов на кодовых шинах 12, 14 (см. фиг, 1, 2) приводит к срабатыванию одного из ключевых интегральных элементов схемы 11, на выходе которого появляется низкий потенциал.

Рабочие потенциалы по шинам 13 поступают на входы одного из транзисторных клю437067

f3

Фиг. Г

5 чей 6 для каждой табличной схемы. Наличие управляющего сигнала на шине 19 приводиг к срабатыванию дешифратора 1 и появлению импульсного сигнала ча кодовых шинах 13, по которым сигнал поступает на вход одного из транзисторных формирователей 5 (для каждой табличной схемы) .

Таким образом, транзисторы единственного формирователя 5 и ключа 6 в каждой табличной схеме отпираются, и в соответствующей первичной обмотке координационно-узлового трансформатора 7, общей для включенных схем, возникает токовый импульс. Токовый импульс во вторичной обмотке пройдет через один из диодов 8 сборки, который кодовым проводом ПКЛ 9 предварительно выбранной ключевой интегральной схемой 11 подключен к общей земляной шине, С выходов ПКЛ 9 на узел усилителей 10 считывания параллельно поступает группа сигналов, соответствующая единственному коду результата.

Предмет изобретения

Побайтный преобразователь из двоичного в двоично-кодированное остаточное представление, содержащий дешифратор байта, диодные сборки и модульные табличные схемы сложения, отличающийся тем, что, с целью упрощения преобразователя и повышения его быстродействия, выходы дешифратора, соот10 ветствующие трем младшим разрядам байта, соединены с первыми входами всех табличных схем сложения, выходы дешифратора, соответствующие четырем старшим разрядам байта, соединены через первую группу диодных

15 сборок со вторыми входами, а через вторую группу диодных сборок — с третьими входами соответствующих табличных схем сложения, а шина четвертого разряда байта соединена с третьими ключевыми входами всех таблич20 ных схем сложения.

437067

785

78 5

15 г

16 3

6гг

12 26

79 6 гг9

73 17 г6 г

23 70

77 Ч

iS5

791 6

7Ч 7

27 гч л г78

7 5 гг

7г

25 12

79 б

70 26

1б 3 гп 7

26 73

23 70

27 8

17 27

17 IIL

71Ч гФ 71

78 5

27 В

72 2В

730

25 12 гг9

2 75

23 10

Ю 76

277 11

26 73

28

1 17

25 12

2 7Ч

271 71

27 8

- 10

2 18

28 15

25 12

26 13

70

D 76

3 79

2 1Ч

77 Ч

18 5

7 7

7г

0 16

25 72 28 15 г 18

5 21

22

26 73 D 76

3 19

1 77

72

27 1Ч

Фиг.3а и 2

В 9

0 г

9 10

3 10 ii

22 Ч

55 7

13 1Ч

15 7б

77

1б 77

17 78

99 77

72

7 10,12

16 19

73) 16

77 11

72 12

21 гг

@7Ч ггпу

19

Фиг 3b

Составитель И. Долгушева

Техред А, Дроздова Корректор А, Дзесова

Редактор А. Батыгин

Заказ 74/15 Изд. № 89 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 5К-35, Раушская наб., д. 4/6

Типография, пр. Сапунова, 2

7 7 9

ВВ 70

13

7Ч

11 12

12 7и гп + г3 70 26 73

2Ч 17 2714