Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

и1 437069

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советским

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 25.09.72 (21) 1830707/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 25.07,74. Бюллетень № 27

Дата опубликования описания 15.01.75 (51) М. Кл, G 061 5/02

Гасударственный комитет

Совета Министров СССР аа делам изобретений и атнрытий (53) УДК 681.325.63 (088.8) (72) Авторы изобретения

Ш. С. Хусаинов и И. И, Городецкий (71) Заявитель (54 ) ПРЕОБРАЗОВАТЕЛЪ ДВОИЧНОГО КОДА

В ДВОИЧНО-ДЕСЯТИЧНЫЙ

Изобретение относится к автоматике и вычислительной технике и предназначено для преобразования кодов.

Известны преобразователи двоичного кода в двоично-десятичный, содержащие двоичный регистр сдвига и двоично-десятичный регистр сдвига со схемами коррекции по числу тетрад.

Цель изобретения †упрости устройство.

Для этого выходы схемы управления вычитанием соединены с соответствующими входами накапливающего сумматора схемы формирования управляющих сигналов и со входами соответствующих групп вентилей, выходы схемы формирования управляющих сигналов соединены со входами схемы управления вычитанием и с одним из входов схемы анализа знака числа, другие входы которой соединены с выходами знакового разряда накапливающего сумматора, а выходы этой схемы соединены со входом схемы управления вычитанием и со счетным входом четырехразрядного двоичного счетчика.

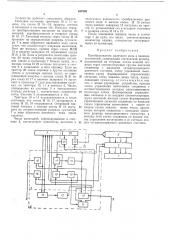

На чертеже изображена схема устройства.

Устройство содержит статический регистр 1, разделенный на тетрады, группы вентилей 2, четырехразрядный двоичный счетчик 3, схему управления вычитанием 4, схему формирования управляющих сигналов 5, схему анализа

6 знака числа, накапливающий сумматор 7, шину подачи тактовых импульсов 8, шину подачи импульса 9 «начало преобразования».

При преобразовании в трехразрядное десятичное число, схема формирования управляющих сигналов 5 реализуется на двух триггерах 10 и 11, элементе задержки 12 и схеме

5 ИЛИ 13, схема управления вычитанием 4 содержит элементы задержки 14 и 15, схемы И

16 — 19; схема анализа 6 знака числа включает в себя триггер 20 знака (накапливающего сумматора 7), схемы И 21 и 22.

10 Устройство реализует следующий алгоритм преобразования.

В сумматор 7 вводится преобразуемое число в двоичном коде, после чего осуществляется последовательное вычитание из числа

15 в двоичном коде его порядка в том же коде до получения младшего порядка. После каждого вычитания анализируется знак остатка числа в сумматоре 7 при помощи схемы анализа 6 и, если число больше нуля, то опера20 ция вычитания повторяется, если же число меньше нуля, то в следующем цикле происходит восстановление остатка, после чего схема формирования управляющих сигналов 5 дает разрешение на вычитание порядка, на едини25 цу меньше 20. Это происходит до тех пор, пока порядок не будет понижен до нуля. Количество вычитаний каждого порядка подсчитывается четырехразрядным двоичным счетчиком 3. После считывания очередного поряд3о ка числа через вентили 2 в статический регистр 1, счетчик 3 устанавливается в «О».

437069

Устройство работает следующим образом.

Исходное состояние триггеров 10 и 11 таково, что схемы И 16 — 19, заперты, счетчик

3 находится в состоянии «О». Импульс «начало преобразования» поступает на триггер 10, который перебрасывается и отпирает схемы

И 16, 17. Тактовый импульс через схему И 16 проходит на определенные разряды сумматора 7 в виде обратного двоичного кода числа

«сто», что соответствует операции вычитания.

Этот же импульс, пройдя через схему ИЛИ

13 и элемент задержки 12, опрашивает схемы

И 21 и 22. Если в результате вычитания триггер 20 знака сохранил свое исходное состояние (число в сумматоре 7 больше нуля), то с выхода схемы И 22 импульс поступает в счетчик 3 и записывает в него единицу. Если же триггер 20 знака перешел в другое состояние (число в сумматоре меньше нуля), то опрашивающий импульс с выхода схемы И 21 через схему И 17 и элемент задержки 14 поступает в сумматор 7 (для восстановления остатка), на триггеры 10, 11 и вентили 2. Число, считываемое из счетчика 3 в определенную тетраду регистра 1, соответствует количеству сотен. Счетчик 3 устанавливается в «О».

Триггеры 10 и 11 устанавливаются в такое состояние, что схемы И 16, 17 запираются, а схемы И 18, 19 открываются. Очередной тактовый импульс с выхода схемы И 18 поступает на соответствующие разряды сумматора

7 в виде обратного двоичного кода числа

«десять».

Число вычитаний, зафиксированное в счетчике 3, соответствует количеству десятков в

10 десятичном эквиваленте преобразуемого двоичного кода, С выхода схемы И 19 сигнал через элемент задержки 15 поступает на триггер 11, устанавливая его в исходное состояние и запирая схемы И 18 и 19.

После понижения порядка числа в сумматоре 7 до нуля, это число, соответствующее количеству единиц, считывается непосредственно из сумматора.

Предмет изобретения

Преобразователь двоичного кода в двоичнодесятичный, содержащий статический регистр, 15 разделенный на тетрады, входы каждой тетрады через соответствующие группы вентилей соединены с выходами четырехразрядного двоичного счетчика, схему управления вычитанием, схему формирования управляющих

20 сигналов, схему анализа знака числа, накапливающий сумматор, отличающийся тем, что, с целью упрощения устройства, выходы схемы управления вычитанием соединены с соответствующими входами накапливающего

25 сумматора схемы формирования управляющих сигналов и со входами соответствующих групп вентилей, выходы схемы формирования управляющих сигналов соединены со входами схемы управления вычитанием с одним из

30 входов схемы анализа знака числа, другие входы которой соединены с выходами знакового разряда накапливающего сумматора, а выходы этой схемы соединены со входом схемы управления вычитанием и со счетным вхо35 дом четырехразрядного двоичного счетчика.