Модель формального нейрона

Иллюстрации

Показать всеРеферат

4Ф воеооюзн;:-: =. яатентно-тс-х "..соийа и от. М

ИЗОБРЕТЕНИЯ р 437I03

Союз СоветскиХ

Социалистически

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 19.04.73 (21) 1908459/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 25.07.74. Бюллетень № 27

Дата опубликования описания 30.12.74 (5I) М. Кл. С 06g 7/60

Государственный комитет

Совета о1иииатров СССР оа делам изаоретений и открытий (53) УДК 681.333(088.8) (»I) Автор изобретения (71) Заявитель

О. Б. Скворцов

Московский ордена Трудового Красного Знамени инженерно-физический институт (54) МОДЕЛЬ ФОРМАЛЬНОГО НЕИРОНА

Изобретение относится к области электрического моделирования и может быть применено в бионике.

В известном устройстве в качестве адаптивного элемента используется переменное сопротивление, что позволяет управлять амплигудой сигналов. Сигналы с различных входов суммируются интегрирующей RC-цепью.

Однако использование в известном устройстве элементов, производимых по различной технологии, а также применение емкости в качестве накопительного элемента делают затруднительным изготовление устройства в монолитном исполнении и затрудняют массовое производство.

Цель изобретения — упростить модель.

Для этого входные цепи выполнены из нечетного числа последовательно соединенных логических элементов И вЂ” HE и инверторов, причем первый элемент имеет два входа, один из которых соединен с выходом последнего элемента, а цепи питания подключены к управляемому генератору тока, вход которого связан с цепями управления весом данного входа, выходы цепочек логических элементов связаны через сумматор со счетчиком. Выход счетчика соединен с управляющим входом генератора выходного импульса.

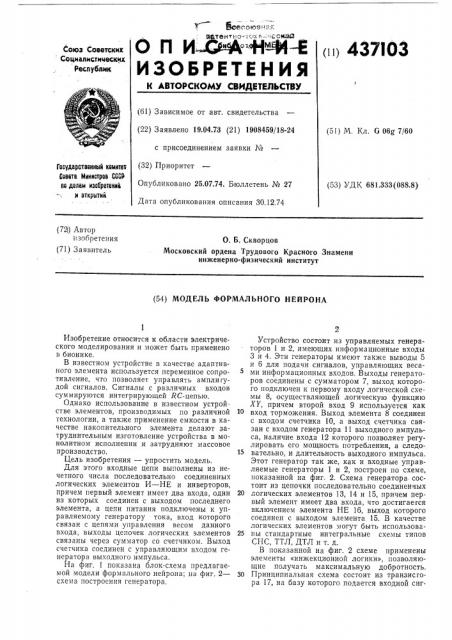

На фиг. 1 показана блок-схема предлагаемой модели формального нейрона; на фиг. 2— схема построения генератора, 2

Устройство состоит из управляемых генераторов 1 и 2, имеющих информационные входы

3 и 4. Эти генераторы имеют также выводы 5 и 6 для подачи сигналов, управляющих весами информационных входов. Выходы генераторов соединены с сумматором 7, выход которого подключен к первому входу логической схемы 8, осуществляющей логическую функцию

ХУ, причем второй вход 9 используется как

10 вход торможения. Выход элемента 8 соединен с входом счетчика 10, а выход счетчика связан с входом генератора 11 выходного импульса, наличие входа 12 которого позволяет регулировать его мощность потребления, а следо15 вательно, и длительность выходного импульса.

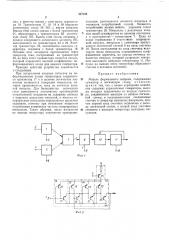

Этот генератор так же, как и входные управляемые генераторы 1 и 2, построен по схеме, показанной на фиг. 2. Схема генератора- состоит из цепочки последовательно соединенных

20 логических элементов 13, 14 и 15, причем первый элемент имеет два входа, что достигаегся включением элемента НЕ 16, выход которого соединен с выходом элемента 15. В качестве логических элементов могут быть использова25 ны стандартные интегральные схемы типов

СНС, ТТЛ, ДТЛ и т. д.

В показанной на фиг. 2 схеме применены элементы «инжекционной логики», позволяющие получать максимальную добротность.

30 Принципиальная схема состоит из транзисгора 17, на базу которого подается входной сиг437103 нал, а эмиттер связан с эмиттером транзистора 18. Транзисторы 17, 18, 19 и 20 образуют логическую схему И вЂ” HE с двумя входами.

Выход этой схемы связан с базой транзистора

21, образующего с транзистором 22 логическую схему НЕ, Выход этой схемы соединен с входом следующего логического элемента НЕ, выполненного на транзисторах 23 и 24. Эмиттер транзистора 24, являющийся выходом генератора, соединен с базой транзистора 18, Питание всех элементов производится через генератор тока, построенный на транзисторе

25, на базу этого транзистора подается сигнал, который определяет весовой коэффициент информационного входа для данного генератора, Принцип действия устройства заключаегся в следующем.

При поступлении входных сигналов на информационные входы генераторов закрывается транзистор 17 и в цепочке логических элементов начинается генерация импульсов, которая продолжается, пока не кончится входной импульс. Для большинства логических схем выполняется постоянство произведения потребляемой мощности на задержку сигнала в широком диапазоне емкостей, а частота генерируемых импульсов определяется временем задержки, поэтому при изменении мощности потребления изменяется частота генерируемых импульсов. Таким образом, число импульсов на выходе генератора получается пропорциональным длительности входного импульса и мощности, потребляемой схемой. Мощность потребленйя можно менять, управляя током транзистора 25. Импульсы с различных входEIbIx цепей суммируются во времени счетчиком, а в пространстве — сумматором 7, Если на входе торможения 9 отсутствует запрещающий импульс, импульсы с сумматора пропускаются логической схемой 8 на вход счетчика

10. После поступления на вход счетчика иекоторого числа импульсов, определяемого коэффициентом пересчета, на выходе счетчика появляется импульс, который разрешает генерацию выходного импульса генератором 11. Им15 пульс на выходе этого генератора сбрасывает счетчик в исходное состояние.

Предмет изобретения

20 Модель формального нейрона, содержащая сумматор и логическую схему, о т л и ч а ющ а я с я тем, что, с целью упрощения модели, она содержит управляемые генераторы, выходы которых подключены ко входам суммаго25 ра, соеДииеяиогб выходом со вХОДом ЛОгической схемы, и последовательно соединенные счетчик и генератор выходных импульсов, причем первый вход счетчика подключен к выходу логической схемы, а второй вход счетчика

30 соединен с выходом генератора выходных импульсов.