Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пп 437I93

Союз Соватсва

--Социалистическими

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 11.09.72 (21) 1827869/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 25.07.74. Бюллетень № 27

Дата опубликования описания 30.12.74 (51) М. Кл. H 031 3/34

Государственный квинтет

Совета Министров СССР

llD делам изооретвни9 и открытий (53) УДК 621.375.024 (088.8) (72) Авторы изобретения

В. В. Меер, В. И. Нестеров и И. В. Баскакова

Особое конструкторское бюро вычислительной техники (71) Заявитель (54) ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ

Изобретение относится .к усилителям и может быть использовано в линейных микросхемах.

Известен дифференциальный усилитель с симметричным входом и несимметричным выходом, содержащий входной дифференциальный каскад, выпол ненный на |полевых тра нзисторах, в общей цепи истоков которых включен источник тока, а в цепи стоков последовательно по постоянному току — первая динамическая нагрузка на полевых транзисторах с объединенными затворами, в цепи стоков которых включена вторая динамическая нагрузка на транзисторах с оо.ьединенными базами, причем между местом соединения затворов и местом соединения баз транзисторов динамических нагрузок включен эмиттерный повторитель, база которого подключена к коллектору одного из транзисторов второй динамической нагрузки, а коллектор другого транзистора упомянутой нагрузки подключен к базе транзистора эмиттерного повторителя выходного каскада.

Однако известный дифференциальный усилитель характеризуется большой чувствительностью статического уровня сигнала на выходе к разбросу напряжения отсечки полевых транзисторов и плохой нагрузочной способностью усилителя, обусловленных нестабильностью режима работы.

Целью изооретения является стабилизация режима работы усилителя.

Это достигается тем, что коллектор эмиттерного повторителя выходного каскада подключен к коллектору эмиттерного повторителя входного каскада, а в цепи коллектора и эмиттера эмиттерного повторителя выходного каскада последовательно по постоянному току включены транзисторы динамических нагру10 зок, базы которых подключены соответственно к общей цепи истоков транзисторов входного дифференциального каскада и через цепь из последовательно соединенных транзистора в диодном включении и резистора к месту соеIS динения без транзисторов второй динамической нагрузки.

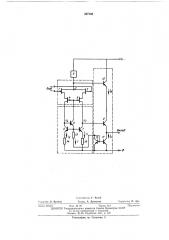

Изобретение поясняется принципиальной схемой. Дифференциальный усилитель с симметричным входом и несимметричным выхо20 дом содержит входной дифференциальный каскад на полевых транзисторах 1, 2, в общей цепи истоков которых включен источник 3 тока смещения, а в цепи стоков,последовательно по постоя иному току — первая дина25 мическая нагрузка,на полевых транзисторах

4, 5 с объединенными затворами, в цепи стоков которых включена вторая динамическая нагрузка на транзисторах 6, 7 с объединен ными базами, эмиттерный повторитель входного

30 каскада на транзисторе 8, эмиттерный повто437193

25

Ю14 I7R„ IR» ритель выходного каскада иа тра|нзисторе 9, в цепи коллектора и эмиттера которого последовательно по постоянному току включены транзисторы 10 и 11 динамических нагрузок соответственно, а также транзистор 12 в диодном включении, резисторы 13, 14 и 15. Между местом соединения затворов полевых транзисторов 4, 5 и местом соединения баз тра нзисторов 6, 7 динамических нагрузок включении эмиттерный повторитель на транзисторе 8, база которого подключена к коллектору транзистора 6 второй динамической нагрузки.

Коллектор транзистора 7 второй ди намической |нагрузки подключен к базе транзистора

9 эмиттерного,повторителя выходного каскада. Коллектор транзистора 9 подключен к коллектору транзистора 8 эмиттер ного повторителя входного каскада. База транзистора 10 динамической нагрузки в цепи коллектора транзистора 9 подключена к общей цепи истоков транзисторов 1, 2 входного:дифференциального каскада. База транзистора 11 динамической нагрузки в цепи эмиттера тра|нзистора 9 подключена через цепь из последовательно соединенных транзистора 12 в диодном включении и резистора 13.к месту соединения баз транзисторов 6, 7 второй динамической нагрузки.

Режим работы усилителя стабилизируется следующи м образом. Благодаря наличию диодно-рези стивной цепи, состоящей из тра нзистора 12 в диод ном включении и резистора

13, создающей смещение на базах транзисторов 6, 7 второй динамической нагрузки имеет место, пропорциональность следующих на пряже,ний: где Ig, Ig — эмиттерные токи транзисторов 6,7;

I — ток через резистор 13;

%з, Ria Ры — сопротивления резисторов 13, 14, 15 соответственно. В то же время нелинейное управление напряжением база-эмиттер ного,перехода транзистора 11 через упомянутую диодно-резистинную цепочку заставляет ток

I«, протекающий через транзистор 11, следить за током 1, так что I«1. В результате этого эмиттерные повторители транзисторов 8 и 9 входного и выходного каскадов одинаково шунтируют транзисторы 6 и 7 второй ди|намической нагрузки, благодаря чему статические напряжения U и U7 на коллекторах соответствующих транзисторов автоматически выравниваются и, соответственно, повышается стабильность работы каскадов. Средний уровень напряжений U6 и U7 стабилизируется следующим образом. Пусть, на пример, на пряжения

Ue и U7 возросли; это приведет к соответствующему изменению токов А, I>, I, 1«, автоматически изменится также ток I

4 цепи транзистора 10 (I

6, 7 второй динамической нагрузки, компенсируя первичное увеличение нанряжений U< и U до их стабилизации.

Описанный процесс стабилизации напряжений U< и U7 возникает при ком пенсации технологических разбросов .на пряжений отсечки полевых транзисторов и тепловом дрейфе источника така. Подключение базы транзистора 10 к общей цепи истоков транзисторов 1, 2 входного дифференциального каскада обеспечивает требуемое автоматическое 1смещение тра|нзисторов 4 и 5 на любом уровне входного сHIlHBJIB U и позволяет использовать транзисторы с одинаковым диффузионным,профилем и ингегральную технологию их изготовления.

Предмет изобретения

Дифференциальный усилитель с симметричным входом и несим метричным выходом, содержащий вход ной дифференциальный каскад, выполненный, например на полевых транзисторах, в общей цепи.истоков которых включен источник тока, а в цепи стоков последовательно по постоянному току — первая динамическая нагрузка,на .полевых транзисторах с объединенными затворами, в цепи стоков которых включена вторая динамическая нагрузка на транзисторах с объединен|ными базами,,причем между местом соединения затворов и местом соединения баз транзисторов динамических .нагрузок включен эмиттерный повторитель, база которого подключена к коллектору одного из транзисторов второй динамической нагрузки, а .коллектор друго го транзистора упомянутой нагрузки подключен к базе транзистора эмиттерного повторителя выходного каскада, отличающийся тем, что, с целью стабилизации режима рабогы усилителя, коллектор эмиттерного:повторителя выход|ного каскада подключен к коллектору эмиттерного повторителя входного,каскада, а в цепи коллектора и эмиттера эмиттерного повторителя выход ного каскада последова тельно IIQ постоянному току включены трап. зисторы динамических нагрузок, базы которых подключены соответственно к общей цепи истоков транзисторов входного дифференпиального каскада и через цепь из последовательно соединенных транзистора в диодном включении и резистора к месту соединения баз транзисторов второй динамической нагрузки.

437193

Юх@Р

Составитель Г. Челей

Техред A. Дроздова

Корректор H. Аук

Редактор О. Кунина

Типография, пр. Сапунова, 2

Заказ 3503, 9 Изд. ¹ 79 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, >К-35, Раушская наб., д. 475