Частотно-фазовый селектор

Иллюстрации

Показать всеРеферат

ОЛИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

00 4372I1

Союз Caserane

Социалистическим

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 25.04.72 (21) 1778642/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 25,07.74. Б|оллетепь № 27

Дата опубликования описания 30.12.74 (51) М Кл. Н 03k 5/18

Государственный комитеФ

Совета Министров СССР ло делам изооретвиие и открытий (53) УДК 621.374.33 (088.8) (72) Авторы изобретения

Б. Г. Шумихин, А. П. Пойда н Н. И. Бараников

{71) Заявитель фЩ « 9 (54) ЧАСТОТНО-ФАЗОВЪ|Й СЕЛЕКТОР

Изобретение относится к вычислительной технике и может быть использовано в устройствах,для автоматического управления и регулирования с частотно-и мпульсным представлением информации.

В известных устройствах используют пересчетные схемы с временньгми задержками на реактивных элементах.

Однако из|вестные устройства имеют сложную схему.

Целью изобретения является упрощениеустройства.

Для этого входы селектора соединены через схему «ИЛИ» со входом триггера обратной связи, вход установки «О» которого,подключен к выходу селектора, а выход триггера соединен с шиной сброса триггеров.

Изобретение пояонено чертежами.

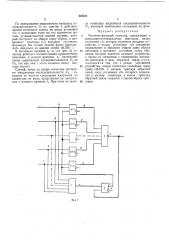

На фиг. 1 приведена блок-схема селектора; на фиг. 2 †.временные диаграммы.

Частотно-фазовый селектор содержит схему «ИЛИ» 1, схему «И» — «НЕ» 2, триггер обратной связи 3, импульсно-потенциальные триггеры 4 (n триггеров) .

Селектор работает следующим образом.

В исходном состоянии на единичных выходах триггеров 4 действует логический нуль, а на выходах схем «ИЛИ» 1 и «И вЂ” НЕ» 2— логическая единица. В момент времени t< (см. фиг. 2) первый импульс последовательности U„поступает,на вход триггера 4 — 1 и, пройдя через схему «ИЛИ» 1, на вход триггера 3, устанавливая на их единичных выходах высокий поигенциал. Управление триггерами 4

5 осуществляется путем подачи на их входы нулевых потенциало в.

Затем поступающие импульсы последовательностей U;, U, устана вливают на единич10 ных выходах триггеров 4=2 — 4= (и — 1) высокий потенциал и подтверждают состояние т.риггера 3.

Наконец, импульс последовательности U„, имеющий низшую частоту, уста навливает вы15 сокий потенциал,и на единичном выходе триггера 4=n. С этого момента триггеры 4=1—

4=n на единичных выходах имеют высокие потенциалы, которые подаются на |входы схемы 2, вследствие чего на ее выходе устанав20 ливается низкий потенциал, который подается на вход установки «О» триггера обратной связи 3.

Так как в это же время импульс последовательности U„, пройдя через схему «ИЛИ» 1, 25 поступает на вход установки «1» триггера 3, который принимает состояние, двух логических единиц на своих выходах. Таким образом триггер 3 не может возвратить триггеры 4 в исходное состояние в течение времени дейст30 вия выделяемого импульса, 437211

По прекращении выделяемого импульса последовательности Uz IHa триггер 3 действует низкий потенциал только .на,входе установки

«0» и вследствие этого на его единичном выходе устанавливается низкий уровень, который поступает на общую шину сброса, и возвращает триггеры 4 в исходное состояние, формируя тем самым задний фронт выделяемого импульса на выходе схемы «ИЛИ» 1.

В интервале времени 4 — 4 (см. фиг. 2) селектор, работает соответственно, приведенному описанию, в момент времени 4 происходит смена выделяемой последовательности U, Hà

Ug, так как она с этого момента имеет низшую частоту.

Случай, когда на входы селектора,поступают иипульоные носледовательности Ug... Up, равные по частоте следования импульсов, но сдвинутые по фазе, представлен на диаграммах с момента времени 4. При этом на выходе селектора выделяется последовательность

U,„èìåþùàÿ наибольшее отставание по фазе.

Предмет изобретения

Частотно-фазовый селектор, содержаш ий и импульсно-нотен циальных триггеров, входы установки «1»;которых являются входами устройства, а входы установки «0» соединены параллельно и образуют общую шину сброса

10 триггеров в исходное состояние, схему «И», выход которой является выходом устройства, а входы ее соединены с единичными выходами триггеров, и цепь обратной связи, отличающийся тем, что, с целью у прощения

15 устройства, входы селектора соединены через схему «ИЛИ» с входом триггера обратной связи, вход установки «О» которого подключен к выходу селектора, а выход триггера обратной связи соединен с шиной-сброса триг20 геров.

437211

Фиг. 2

Составитель М. Панкратов

Редактор А. Зиньковский Техред А. Дроздова Коррек-.ор Л. Царькова

Заказ 3503713 Изд. ¹ 79 Тираж 811 Подписное

1\НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, _#_-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2