Цифровой делитель частоты с дробным коэффициентом деления

Иллюстрации

Показать всеРеферат

п 437224

Союз Соввтских

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 29.03.73 (21) 1902217/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 25.07.74. Бюллетень № 27

Дата опубликования описания 26.12.74 (51) М. Кл. Н 031 23/00

ГввтАйрвтвениый ивмитвт

Совета Мииистрвв СССР а делам изобретеиий и иткрытий (53) УДК 621.374.4 (088.8) (72) Авторы изобретения

М. Я. Минц, В. Н. Чинков и В. T. Рябуха (71) Заявитель (54) ЦИФРОВОЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ

КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

А=а, + аа+

N — = — а,+ У

Уi Vt

У1 . У

2+

»

Уа Уа

25 (2) Vi i, Vi+i

=alw

Vi Уi

Vn

= а„+1, Уп+1

Изобретение может применяться в радиоэлектронике, вычислительной и цифровой электроизмерительной технике.

Известны цифровые делители частоты с дрббным коэффициентом деления, содержащие п пересчетных схем со схемами блокирования на входе.

Цель изобретения — повысить точность, расширить частотный диапазон и упростить устройство.

Предлагаемый делитель отличается от известных тем, что в нем выход первой пересчетной схемы соединен со входом второй схемы блокирования, выход i-той пересчетной схемы (i = 2, 3,..., n — 1) соединен со входами (i — 1)-ой и (i + 1)-ой схем блокирования, выход п-ой пересчетной схемы соединен со входом (n — 1-)-ой схемы блокирования и со входом (и+ 1)-ой пересчетной схемы, выход которой соединен со входом п-ой схемы блокирования.

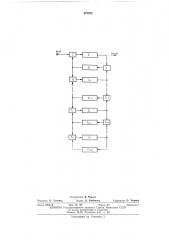

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит схемы блокирования

lь lе,..., 1;..., 1„0 l„и пересчетные схемы

2i 2 » ° ° ° 2; ° ° ° 2»» 2и+-1 °

Коэффициенты пересчета схем 2,, 2,...

2,,... 2» 2 +1 выбираются равными коэффициентам разложения аь а,... а;,... a, a+< требуемого коэффициента деления и в цепную дпобь

1 аз+ — +... а

4 ад )

Тогда при подаче на вход делителя N импульсов на его выходе появляется число им/1V пульсов у, = E — ), где E — целая часть

10 )

N числа и

Для доказательства этого утверждения рассмотрим алгоритм Эвклида.

Известно, что алгоритм Эвклида приводит к зацепляющейся системе уравнений с известнымн коэффициентами аь а,..., а;... а„+ь являющимися коэффициентами разложения величины и в цепную дробь (1)

20 1

437224 у,., — у + =- a,у, или

Уi — s — Уi-, i (3) Ую=

55 где i = 1, 2,... и + 1;

g, Л, у„, O, a,=-E(k).

В этой системе уравнений уя(у уз(уз ° » у (ус i уи(у » .

Запишем систему уравнений (2) в виде:

Для решения системы уравнений (3), очевидно, необходимо каждым импульсом у; из последовательности N заблокировать (вычесть) один импульс у; и полученное разностное число импульсов (у; f — у;+<) разделить на коэффициент а;.

В предложенной схеме делителя операция блокирования (или вычитания) импульса у; осуществляется при помощи схемы блокирования 1;, соединяющей выход пересчетной схемы 2; < со входом пересчетной схемы 2, и управляемой выходным сигналом пересчетной схемы 2;ьь Эту операцию можно осуществить, если схему блокирования 1; закрывать выходным импульсом пересчетной схемы 2;+ и открывать поступающим после этого очередным импульсом с выхода пересчетной схемы 2; ь

Принцип действия предлагаемого устройства заключается в следующем.

В исходном состоянии все схемы блокирования 1; открыты.

При поступлении через схему блокирования

1> на вход пересчетной схемы 2> первых а> импульсов из числа A на выходе пересчетной схемы 2> формируется импульс переполнения.

Этот импульс является выходным импульсом делителя.

Кроме того, этот же импульс через схему блокирования 1 поступает на вход пересчетной схемы 2, имеющей коэффициент пересчета а . При поступлении а импульсов на вход схемы 2> на ее выходе появляется импульс переполнения. Этот импульс через открытую схему блокирования 1, поступает в пересчетную схему 2З с коэффициентом пересчета аз и закрывает схему блокирования 1 на один входной импульс, которым она возвращается в открытое состояние. Очередной импульс на выходе схемы 2 появится через a> — 1 входных импульсов делителя. На выходе пересчетной схемы 2> импульс переполнения сформируется после поступления на ее вход с выхода схемы 2 числа импульсов аз. Этот импульс посредством схемы блокирования 1> блокирует один входной импульс схемы 2 .

Таким образом, предлагаемым делителем решается система уравнений (3). Это означает, что при поступлении на вход делителя числа импульсов,N íà его выходе формируется число импульсов уь причем отклонение среднего значения частоты, получаемой в процессе деления, от истинного минимальное.

Входная частота делителя ограничивается только быстродействием пересчетных схем, как любой последовательной схемы деления, и не зависит от переходных процессов в них.

Действительно, наиболее критичной к частоте входных импульсов является схема блокирования l ь Но поскольку заблокированным может быть любой из L (k) импульсов, то фактически работа схемы блокирования 1 переводится в область более низкой частоты, а именно в F® раз меньшей входной частоты делителя.

Предлагаемый делитель более точен, чем известный, благодаря тому, что в нем задержка выходного импульса обусловлена временем переходных процессов одной пересчетной схемы, содержащей не более четырех ячеек.

А поскольку для последовательной пересчетной схемы время задержки всегда постоянно, то можно считать, что, во-первых, погрешность смещения в данной схеме отсутствует, и, во-вторых, отсутствует дополнительная частотная модуляция за счет временной нестабильности появления импульсов.

И, наконец, весьма очевидна простота схемной реализации предлагаемого делителя, так как в качестве пересчетных схем могут быть использованы любые декадные делители частоты с переменным коэффициентом деления.

Предмет изобретения

Цифровой делитель частоты с дробным коэффициентом деления, содержащий и пересчетных схем со схемами блокирования на входе и (n + 1) -ю пересчетную схему, о т л ич а ю шийся тем, что, с целью повышения точности, расширения частотного диапазона и упрощения, выход первой пересчетной схемы соединен со входом второй схемы блокирования, выход i-той пересчетной схемы (i =

=2, 3,..., n — 1) соединен со входами (— 1) -ой и (i + 1) -ой схем блокирования, выход и-ой пересчетной схемы соединен со входом (n — 1)-ой схемы блокирования и со входом (n+ 1)-ой пересчетной схемы, выход которой соединен со входом и-ой схемы блокирования.

437224

5c iyOp

Составитель В. Чинков

Корректор О. Тюрина

Техред В. Рыбакова

Редактор О. Степина

Типография, пр. Сапунова, 2

Заказ 3464/18 Изд. Ие 107 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д, 4/5