Устройство для регистрации ошибок

Иллюстрации

Показать всеРеферат

ес:ою=Вф @еетмс-. ">.

О П И С А Н И Е (и) 437236

ИЗОБРЕТЕ HH$

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сове Советских

Социалистических

Ресоублик (61) Зависимое от авт. свидетельства (22) Заявлено 07.04.72 (21) 1769354/26-9 с присоединением заявки № (51) М. Кл. Н 041 1 04

Совета ейинистров СССР ло делам изобретений и открытий

Опубликовано 25.07.74. Бюллетень № 27

Дата опубликования описания 19.02.75 (53) УДК 621.394.5.18 (088.8) (72) Авторы изобретения

Ю. И. Калганов и В. Т. Хрыкии (71) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ОШИБОК

Государственный комитет (32) Г1риоритет

Изобретение относится к радиотехнике и может быть использова но для регистрации и анализа ошибок при приеме дискретных сигналов по высокоскоростным каналам связи.

Известны устройства для регистрации ошибок, содержащие блок фазирования и выделения ошибок, к выходу которого подключен распределитель, соединенный с разрядами анализатора смежных ошибок, и счетчики, подключенные к выходам этих разрядов. Однако известные устройства характеризуются ограниченным быстродействием.

Цель изобретения — повысить быстродействие устройства.

Для этого вводят высокочастотные элементы обработки дискретных сигналов, которые позволяют повысить быстродействие устройства для использования его в наносекундном диапазоне.

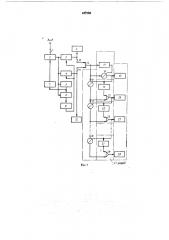

В предлагаемом устройстве распределитель содержит последовательно включенную цепочку каскадов запрета, подключенную к выходу каскада «ИЛИ» блока фазирования и выделения ошибок и к входу первого разряда анализатора смежных ошибок. Выходы каскадов запрета поочередно соединены с входами остальных разрядов анализатора смежных ошибок, причем первый разряд состоит из линии задержки на один тактовый интервал и,каскада запрета, запрещающий вход которого подключен к выходу каскада

«ИЛИ» через линию задержки. Второй вход каскада запрета первого разряда непосредственно подключен к выходу каскада «ИЛИ».

Выход каскада запрета первого разряда соединен с запрещающим входом каскада запрета распределителя, с входом линии задержки второго разряда анализатора и с входом счетчика. Каждый из остальных разрядов аналиl0 затора смежных ошибок состоит из ли|нии задержки на один тактовый интервал и каскада совпадения, один вход которого подключен через линию задержки к выходу предыдущего .разряда, а другой соединен с выходом кас15 када запрета распределителя. Выход каскада совпадения подключен также к запрещающему входу следующего каскада запрета и к входу счетчика, На фиг. 1,приведена функциональная схема

20 устройства; на фиг. 2 — временные диаграммы напряжений в отдельных точках схемы.

Устройство содержит блок фазирования и выделения ошибок, распределитель, анализатор смежных ошибок и счетчики. В состав

2s блока фазирования и выделения ошибок входят: тумблер 1 включения света, блок 2 анги матической остановки счета, блок выделения ошибок типа (1- -О) 3, блок выделения ошибок типа (Π— +1) 4, блок разрядной синхронизации зс 5, блок цикловой синхронизации 6, счетчик

437236

10

15 тактовых импульсов 7, блок контрольных сигналов 8, счетчик ошибок типа (1 — «О) 9, тумблеры 10 и 11, обеспечивающие возможность исключить из анализа смежных ошибок ошибки типов (1 — «О) или (Π— э1), счетчик ошибок типа (Π— -1) 12, каскад «ИЛИ» 13.

Распределитель состоит из цепочки каскадов запрета 14, 15, 16.

Анализатор смежных ошибок содержит и разрядов (на фиг. 1 показаны 1-ый, 2-ой, 3-ий и и-ый разряды), причем 1-й разряд состоит из линии задержки на один тактовый интервал

17 и каскада запрета 18, а каждый из остальных разрядов — из аналогичной линии задержки 19, 20, 21 и каскада совпадения 22, 23, 24.

Число счетчиков смежных ошибок 25 — 28 равно числу разрядов анализатора.

Устройство работает следующим образом.

Испытательные сигналы из линии поступаюг в блоки выделения ошибок 3 и 4 и поэлементно сравниваются с контрольными кодовыми комбинациями, формируемыми в блоке контрольных сигналов 8. Выделенные импульсы ошибок объединяются в общий поток в каскаде «ИЛИ» 13.

На диаграмме «а» (см. фиг. 2) показана последовательность импульсов ошибок на выходе каскада «ИЛИ» 13, состоящая в данном примере из одиночной ошибки и смежной ошибки длиной а,, =4, разделенных безошибочным интервалом в один такт. Импульсы ошибок поступают на оба входа .каскада запрета 18, причем на запрещающий вход о ни приходят задержанными на один тактовый интервал (фиг. 2, б). На выход каскада запрета 18 и в счетчик первого разряда 25 пропускаются только одиночные ошибки и первые импульсы смежных ошибок (фиг. 2, в). На запрещающий вход каскада запрета 14 распределителя поступают импульсы с выхода первого разряда анализатора смежных ошибок, поэтому на вход второго разряда анализатора не пропускаются одиночные ошибки, а длина смежных ошибок уменьшается на один тактовый интервал. С выхода каскада запрета 14 импульсы ошибок (фиг. 2, г) подаются на вход следующего каскада запрета 19 распределителя и на вход каскада совпадения 22, к второму входу которого подводятся импульсы одиночных ошибок и первые импульсы смежных ошибок, задержанные на один тактовый интервал в линии задержки 19 (фиг. 2, д). Поэтому на вход счетчика второго

50 разряда 26 пропускаются только вторичные импульсы смежных ошибок, в тех случаях, когда они существуют (фиг, 2, е). В остальных разрядах процессы аналогичны процессам во втором разряде. Счетчик третьего разряда

27 служит для регистрации третьих импульсов смежных ошибок и так далее.

Таким образом, в предлагаемом устройстве происходит последовательное опробование

К-х импульсов смежных ошибок (К вЂ” 1) -ми импульсами, задержанными на один тактовый интервал. В счетчике К-го разряда регистрируются смежные ошибки длиной с

Предмет изобретения

Устройство для регистрации ошибок при приеме дискретных сигналов по высокоскоростным каналам связи, содержащее блок фазирования и выделения ошибок, к выходу которого подключен распределитель, соединенный с разрядами анализатора, и,счетчики, подключенные к выходам этих разрядов, о тл и ч а юще е ся тем, что, с целью повышения быстродействия, распределитель содержит последовательно включенную цепочку каскадов запрета, подключенную к выходу каскада «ИЛИ» блока фазирования и выделения ошибок и к входу первого разряда анализатора, а выходы каскадов запрета поочередно соединены с входами остальных разрядов анализатора, причем первый разряд состоит из линии задержки на один тактовый интервал и каскада за,прета, запрещающий вход которого подключен к выходу каскада «ИЛИ» через линию задержки, второй непосредственно подключен к выходу каскада «ИЛИ»,:выход каскада запрета соединен с запрещающим входом каскада запрета распределителя, с входом линии задержки второго разряда анализатора и с входом счетчика, а каждый из остальных разрядов анализатора состоит из линии задержки на один тактовый интервал и каскада совпадения, один вход которого подключен через линию задержки к выходу предыдущего разряда, а другой соединен с выходом каскада запрета распределителя, причем выход каскада совпадения подключен также к запрещающему входу следующего каскада запрета и к входу счетчика.

Составитель Ю. Колганов

Редактор О, Кунина Техред T. Курилко Корректор А. Дзесовя

Заказ 239/6 Изд. № 238 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2