Временной дискриминатор

Иллюстрации

Показать всеРеферат

О П

ИЗОБРЕТЕ Н ИЯ (u) 438l03

Союз Советскии

Социалистических .

Республик .

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое. от авт, свидетельства --=(22) Заявлено 25.05;73 (21) 1925861 26-9 . (51(X Кл. Н 03k 5/18 :с присоединением заявки №

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (32) Приоритет (53) УДК -621.374.33(088;8)Опубликовано 30.07.74. Бюллетень № 28

Дата опубликования описания 27.12.74 (72) Авторы изобретения

А. И. Нагайник, В. П. Гуменюк и В. А. Легостаев (71) Заявитель (54) ВРЕМЕННОЙ ДИСКРИМИНАТОР

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам измерения фазовых сдвигов импульсных сигналов и автоподстройки частоты автогенераторов.

Известны временные дискриминаторы, содержащие R — S-триггеры с раздельными входами и логические схемы «И — HE», через которые выходы одного триггера соединены с входами другого триггера, причем, вторые входы логических схем «И вЂ” HE» подключены к формирователю тактовых импульсов.

Недостаток известных дискриминаторов состоит в том, что они не определяют величину опережения (или отставания) одного сигнала относительно другого и имеют значительное количество элементов, что ухудшает надежность и технологичность, увеличивает габариты и стоимость устройства.

Цель изобретения — упрощение схемы и расширение ее функциональных возможностей.

Эта цель достигается тем, что первый R—

S-триггер выходами соединен соответственно с первыми входами выходных логических схем «И вЂ” НЕ», вход Я упомянутого триггера соединен с вторыми входами, а вход S— с третьими входами выходных логических схем «И вЂ” НЕ», выходы которых подключены соответственно к входам R u S второго

R — S-триггера.

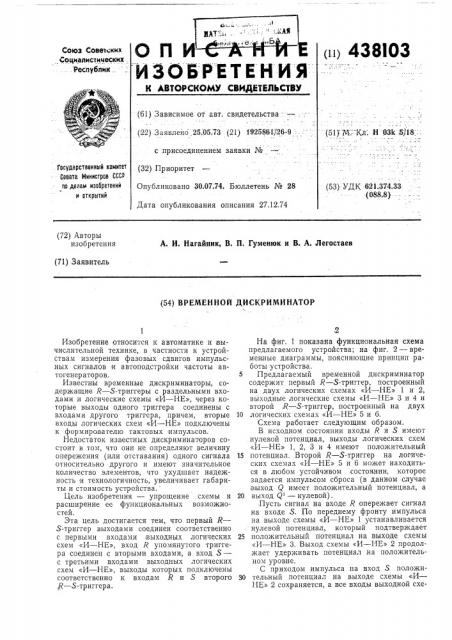

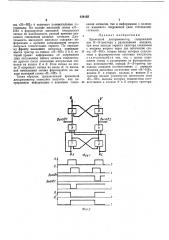

На фиг. 1 показана функциональная схема предлагаемого устройства; на фиг. 2 — временные диаграммы, поясняющие принцип работы устройства.

5 Предлагаемый временной дискриминатор содержит первый R — S-триггер, построенный на двух логических схемах «И — НЕ» 1 и 2, выходные логические схемы «И — HE» 3 и 4 и второй R — S-триггер, построенный на двух

10 логических схемах «И — НЕ» 5 и 6.

Схема работает следующим образом.

В исходном состоянии входы R u S имеют нулевой потенциал, выходы логических схем

«И — HE» 1, 2, 3 и 4 имеют положительный

15 потенциал, Второй R — S-триггер на логических схемах «И — НЕ» 5 и 6 может находиться в любом устойчивом состоянии, которое задается импульсом сброса (в данном случае выход Q имеет положительный потенциал, а

20 выход Q — нулевой) .

Пусть сигнал на входе R опережает сигнал на входе S. По переднему фронту импульса на выходе схемы «И — HE» 1 устанавливается нулевой потенциал, который подтверждает

25 положительный потенциал на выходе схемы

«И — НЕ» 3. Выход схемы «И — НЕ» 2 продолжает удерживать потенциал на положительном уровне.

С приходом импульса на вход S положи30 тельный потенциал на выходе схемы «И—

НЕ» 2 сохраняется, а все входы выходной схе438103 фыхо

4 иг.2

3 мы «И — HE» 4 получают положительные потенциалы. На выходе выходной схемы «И—

НЕ» 4 формируется выходной импульсный сигнал по длительности, равный времени взаимного совпадения входных сигналов. Длительность выходного имлульса содержит информацию о времени запаздывания второго импульса относительно первого. По переднему фронту выходного импульса опрокидывается триггер на схемах «И — НЕ» 5 ии 66, который хранит информацию об опережении (или отставании) одного сигнала относительно другого после окончания импульсных сигналов на входах R u S. Если сигнал на входе S опережает сигнал на входе Я, то выходной импульсный сигнал формируется на выходе выходной схемы «И — НЕ» 3.

Таким образом, предлагаемый временной дискриминатор позволяет получить как непрерывную информацию о взаимном следо4 ванин сигналов, так н информацию о величине взаимного опережения (или отставания) сигналов.

5 Предмет изобретения

Временной дискриминатор, содержащий два R — S-триггера с раздельными входами, при этом выходы первого триггера соединены с входами второго через две логические схе10 мы «И — НЕ», вторые входы которых подключены к формирователю тактовых импульсов, отличающийся тем, что, с целью упрощения схемы и расширения ее функциональных возможностей, первый R — S-триггер вы15 ходами соединен соответственно с первыми входами выходных логических схем «И вЂ” НЕ», входом Rквторым входам,,а входом $ к третьим входам упомянутых логических схем

«И — НЕ», выходы которых подключены соот20 ветственно к входам R u S второго триггера,