Четырехтактный динамический регистр на мдп-транзисторах

Иллюстрации

Показать всеРеферат

:. СЕСО)ОЗИМ лт .. . бибвн;(

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п1) 438I06

СОЮЗ СОВетскин

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 23.01.73 (211) 1873281 26-9 с присоединением заявки № (32) Приоритет

Опубликовано 30.07.74. Бюллетень № 28

Дата опубликования описания 10.01.75 (51) М, Кл. Н 03k 13/258.Государственный комитет

Соватв Министров СССР до делам иэооретеннй и открытий (53) УДК 681.326.33 (088.8) (72) Автор изобретения

В. И. Шагурин (71) Заявитель

Московский ордена Трудового Красного Знамени инженернофизический институт (54) ЧЕТЫРЕХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР

НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к устройствам микроэлектроники и может использоваться в интегральных схемах со структурой МДП для реализации последовательных запоминающих устройств, линий задержки, регистров среднего и высокого быстродействия.

Известен четырехтактный динамический регистр сдвига на МДП-транзисторах, в котором безусловная зарядка запоминающего конденсатора осуществляется через транзистор в диодном включении.

Недостатки известного регистра состоят в том, что максимальное быстродействие его невелико и ограничено минимально допустимой длительностью импульсов в фазах «а» и «в», которая, в свою очередь, зависит от времени зарядки запоминающего конденсатора через зарядный транзистор, включенный по диодной схеме с высоким импедансом; устройство содержит большое число транзисторов и занимает значительную площадь на полупроводниковом кристалле.

Цель изобретения повышение быстродействия и уменьшение площади регистра, занимаемой на кристалле за счет сокращения числа транзисторов.

Эта цель достигается тем, что в каждом каскаде зарядный транзистор заменен зарядным конденсатором. Заряд запоминающего конденсатора производится через емкостной делитель и диод, образованный p — и-переходом, ограничивающим область стока МДПтранзистора, причем на тактовый вход каскада подается импульс напряжения, прямо смещающего указанный диод.

В результате удалось заменить высокоомную цепь заряда запоминающего конденсатора цепью с весьма низким импедансом, вследствие чего стало возможным более чем на порядок уменьшить длительность тактового импульса, заряжающего запоминающий конденсатор и таким образом повысить рабочую частоту регистра, а также сократить число транзисторов в схеме на одну треть.

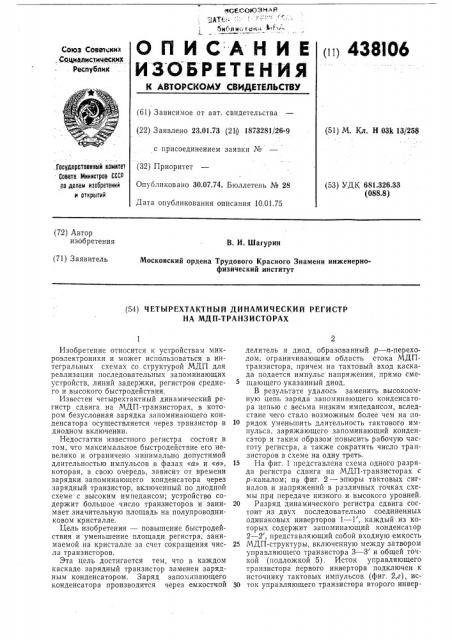

15 На фиг, 1 представлена схема одного разряда регистра сдвига на МДП-транзисторах с р-каналом; на фиг. 2 — эпюры тактовых сигналов и напряжений в различных точках схемы при передаче низкого и высокого уровней.

20 Разряд динамического регистра сдвига состоит из двух последовательно соединенных одинаковых инверторов 1 — 1, каждый из которых содержит запоминающий конденса1ор

2 — 2, представляющий собой входную емкость

25 МДП-структуры, включенную между затвором управляющего транзистора 3 — 3 и общей точкой (подложкой 5) . Исток управляющего транзистора первого инвертора подключен к источнику тактовых импульсов (фиг. 2,г), ис30 ток управляющего транзистора второго инвер438106

15 тора подключен к источнику тактовых импульсов (фиг. 2,б). Последовательно с управляющим транзистором в каждом инверторе включены транзисторы 4 — 4 и зарядные конденсаторы 6 — 6 . Затвор ключевого транзистора 4 и зарядный конденсатор 6 первого инвертора подключены соответственно к генераторам импульсов б и а, а затвор ключевого транзистора 4 и зарядный конденсатор 6 второго инвертора — к генераторам импульсов г и 8.

Входом каждого из инверторов являются затворы управляющих транзисторов 3 — 3 . Выходами каждого из инверторов служат средние точки ключевых транзисторов и зарядных конденсаторов, к которым подключены паразитные диоды 7 — 7, образованные границей раздела стоковых областей ключевых транзисторов и подложки 5.

Устройство работает следующим образом.

Если в исходный момент на входе действует низкий уровень напряжения (фиг. 2,д), то транзистор 3 в первом каскаде заперт. Положительный тактовый импульс (фиг. 2,a) через диод 7 и сопротивление толщи подложки заряжает конденсатор 6. По окончании импульса (фиг. 2,а) диод 7 запирается, а обкладка конденсатора 6, подключенная к генератору, оказывается заземленной через внутреннее сопротивление генератора. На выходе первого инвертора возникает отрицательный потенциал, величина которого определяется амплитудой тактового импульса и коэффициентом передачи емкостного делителя 2 — 6 и превышает пороговое напряжение МДП-структуры. Отпирание ключевого транзистора 4 тактовым сигналом (фиг. 2,б) в первом каскаде не приводит к изменению напряжения на выходе последнего, вызывая лишь незначительную импульсную помеху, так как транзистор 3 заперт.

Таким образом, в течение первого полупериода тактовых импульсов на выходе первого инвертора формируется потенциал, отпирающий транзистор 3 во втором инверторе (фиг. 2,г). Тактовый импульс (фиг. 2,в), действующий во втором инверторе на одну из обкладок конденсатора 6, заряжает последний г0

45 через диод 7, однако по окончании импульса (фиг. 2,в) конденсатор 6 быстро разряжается по цепи: транзистор 4, открытый импульсом (фиг. 2,г), транзистор 3, открытый сигналом с выхода первого инвертора (фиг. 2,г), и внутреннее сопротивление генератора импульсов (фиг. 2,б). Таким образом, через промежуток времени, равный периоду тактовых импульсов на выходе второго инвертора возникает информация, эквивалентная входной информации на первом инверторе (фиг. 2,х).

Аналогичные процессы в устройстве протекают при передаче высокого уровня напряжения. Таким образом, в течение периода тактовых импульсов в резисторе происходит сдвиг информации на один разряд.

Предмет изобретения

Четырехтактный динамический регистр на

МДП-транзисторах, содержащий четыре тактовых шины, два инвертора, каждый из которых выполнен на запоминающем конденсаторе, управляющем и ключевом транзисторах, причем в первом инверторе затвор и сток управляющего транзистора подключены соответственно к входной шине и к истоку ключевого транзистора, затвор и сток которого соединены соответственно с второй тактовой шиной и запоминающим конденсатором, а во втором инверторе затвор и сток управляющего транзистора подключены соответственно к выходу первого инвертора и к истоку ключевого транзистора, затвор и сток которого соединены соответственно с четвертой тактовой шиной и запоминающим конденсатором, отлич а ю щи и с я тем, что, с целью повышения быстродействия регистра, первая и третья тактовые шины через дополнительно установленные зарядные конденсаторы подключены к стокам ключевых транзисторов и запоминающим конденсаторам соответственно первого и второго инверторов, а стоки управляющих транзисторов первого и второго инвер торов подключены соответственно к четвертой и второй тактовым шинам.

438106

- ч

1 (I ж( г (!

1 б (г

I ! Ю! !

-! (1 ! !

Фиг.1

Тгеиврадар

Пггне аща

ЩИНгРапЮР 8,Йаенюратр

Составитель В. Шагурин

Техред 3. Тараненко

Корректор Т. Хворова

Редактор М. Бычкова

Заказ 3585/2 Изд. № 1845 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2