Элемент для согласования насыщенных и ненасыщенных логических схем

Иллюстрации

Показать всеРеферат

i 438II9

ОП И

ИЗОЬРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 19.07.72 (21) 1812536/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 30.07.74. Бюллетень № 28

Дата опубликования описания 10.01.75 (51) М. Кл. Н 03k 19/00

Гааудваственный квинтет

Саввта й1иннстрав СССР на делам изоеретений и атнрытий (53I) УДК 621.374(088.8) (72) Авторы изобретения

В. И. Лебедев и В. А. Лукьянов

Московский ордена Трудового Красного Знамени инженернофизический институт (71) Заявитель (54) ЭЛЕМЕНТ ДЛЯ СОГЛАСОВАНИЯ НАСЫЩЕННЫХ

И НЕНАСЫЩЕННЫХ ЛОГИЧЕСКИХ СХЕМ

Изобретение относится к цифровой автоматике и вычислительной технике и может использоваться для согласования логических уровней насыщенных элементов типа ТТЛ (транзисторно-транзисторная логика), ДТЛ (диодно-транзисторная логика) и других с логическими уровнями элементов ненасыщенной транзисторной логики на переключателях тока (ТЛПТ) при использовании указанных элементов в пределах одной системы, а также для повышения запаса помехоустойчивости при использовании элемента согласования в качестве буферного элемента на входе системы, построенной на элементах ТЛПТ. Элемент может также применяться для согласования уровней в операционных и других усилителях.

Известна транзисторная логическая схема, имеющая аналогичное назначение. На входе этой схемы для выполнения логической функции «И» установлен многоэмиттерный транзистор (МЭТ), на эмиттеры которого подаются входные сигналы, а база через сопротивление связана с шиной питания + Е„. Коллектор

МЭТ связан с базой эмиттерного повторителя, коллектор которого через ограничивающее сопротивление подключен к шине +Е, а эмиттер связан с короткозамкнутыми базой и коллектором другого МЭТ, один из эмиттеров которого подключен к нулевой шине, а другой связан с шиной питания — Е; через два последовательно включенных резистора, точка соединения которых является выходом логической схемы, Недостаток этой схемы состоит в недостаточной точности фиксации логических уровней при изменении напряжения смещения, температуры среды и при разбросе параметров схемы, а также в относительно низком быстродействии, обусловленном тем, что транзистор повторителя попадает в область насыщения, работая в режиме фиксации эмиттерного напряжения и ограничения коллекторного тока; рассасывание избыточного заряда и перезаряд динамической коллекторной емкости приводят

15 к увеличению задержки в передаче сигнала.

Цель изобретения — построение элемента для согласования насыщенных и ненасыщенных логических схем, обеспечивающего согласование уровней в широком температурном

20 диапазоне при изменении питающих напряжений и разбросе параметров.

Поставленная цель достигается тем, что элемент содержит диодный стабилизатор, два транзистора связи в диодном включении и ге25 нератор тока на транзисторе, база которого подключена к источнику опорного напряжения, а коллектор — к выходной шине; два транзистора связи включены между выходной шиной и коллектором входного многоэмиттерЗО ного транзистора, точка соединения транзи438119

3 сторов связи подключена через диодный стабилизатор к общей шине.

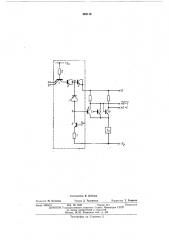

Изобретение поясняется чертежом.

На входе схемы установлен многоэмиттерный транзистор 1, на эмиттеры которого подаются входные сигналы, а база через резистор 2 подключена к шине коллекторного питания. Коллектор многоэмиттерного транзистора соединен с выходной шиной элемента через два последовательно включенных транзистора 3 и 4 в диодном включении, точка соединения которых через транзистор 5, являющийся стабилизатором, связана с нулевой шиной питания. К выходной шине подключен генератор тока, обеспечивающий протекание тока через транзисторы 3 и 4 в любом логическом состоянии и состоящий из транзистора

6, на базу которого подается опорное напряжение, а эмиттер через резистор 7 связан с шиной эмиттерного питания.

При подаче на входы А и В логической единицы, т. е. высокого уровня, эмиттерные переходы транзистора 1 смещаются в обратном направлении, напряжение на базе и коллекторе его, а также в точке т повышается. Транзистор 5 фиксирует потенциал точки т на уровне U =Uaэ и обеспечивает тем самым потенциал в точке б, равный нулю, так как падение напряжения на транзисторе связи 4 также равно Ua Если использовать интегральные транзисторы 4 и 5, расположенные в одном кристалле и имеющие относительно малый разброс напряжений и их температурных коэффициентов, то можно получить высокую степень компенсации температурных изменений параметров транзисторов 4 и 5. Следовательно, потенциал выходной шины фиксируется на уровне логической единицы (высокий уровень, равный в данном случае нулю вольт) с высокой точностью и обеспечивает включение транзистора 8 элемента ТЛПТ.

При подаче на один из выходов (А или В) низкого уровня, т. е. логического нуля, напряжение на базе и коллекторе многоэмиттерного транзистора, а также в точках т и б уменьшится примерно на величину 2Uq,. При этом условие выключения элемента ТЛПТ

U x (— 0,3 в всегда надежно выполняется.

Уровень логического нуля может быть при необходимости ограничен включением диода между точкой б и шиной земли.

Особенностью схемы является также сравнительно быстрая коммутация сигналов, так как коллекторный переход МЭТ открыт в обоих состояниях элемента, обеспечивая вместе с генератором тока быстрый перезаряд емкостей (C„+Cð) транзистора 5 и емкости нагрузки. Напряжение на транзисторах 3 и 4 во время переключения практически не изме5

З0

40 няется, что содействует увеличению быстродействия схемы. При этом суммарная емкость переходов (CÄ+C,) транзисторов 3 и 4 выполняет функцию ускоряющей емкости, обеспечивая форсированную передачу на выход фронтов сигнала.

При использовании элемента согласования в субсистеме типа микромощного счетчика или регистра один элемент согласования обслуживает всю субсистему, обеспечивая повышение запаса помехоустойчивости по ее входу до

0,8 в с уровня 0,2 в, который имела бы субсистема без элемента согласования. Обработка информации в субсистеме происходит на регенеративных элементах ТЛПТ, аналогичных элементу, показанному на чертеже (транзисторы 8, 9, 10). Выход субсистемы согласуется с нагрузкой или с насыщенными элементами с помощью буферного каскада. Такая организация субсистемы БИС в целом обеспечивает совмещение высокого запаса помехоустойчивости по входу и выходу с низким уровнем потребляемой мощности в цепях обработки информации.

Элементы согласования вместе с элементом

ТЛПТ могут выполнять самостоятельные логические функции, например, при проектировании сумматора. Для этого к дополнительному входу элемента ТЛПТ подключается элемент согласования со входами D и Е. Тогда на выходе элемента ТЛПТ получается функция (АВ+РЕ) и AB+DE (где для случая полусумматора Р=А, В=Е). Расширение логических функций может осуществляться и для большего числа переменных.

Элемент согласования был испытан при работе со счетчиком на ТЛПТ элементах и показал нормальную работоспособность в температурном диапазоне — 60 — + 125 С.

Предмет изобретения

Элемент для согласования насыщенных и ненасыщенных логических схем, содержащий входной многоэмиттерный транзистор, о т л ич а ю шийся тем, что, с целью обеспечения согласования уровней в широком температурном диапазоне при изменении питающих напряжений и разбросе параметров, элемент содержит диодный стабилизатор, два транзистора связи в диодном включении и генератор тока на транзисторе, база которого подключена к источнику опорного напряжения, а коллектор — к выходной шине и к коллектору входного многоэмиттерного транзистора через два последовательно включенных транзистора связи, точка соединения которых через диодный стабилизатор подключена к общей шине.

438119

Корректор T. Хворова

Редактор М. Бычкова

Заказ 3585/15 Изд. № 1845 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2

Составитель В. Лебедев

Техред 3. Тараненко ив+с ив+с