Устройство для контроля радиоканала передачи данных с трансформацией скоростей манипуляции

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

438127

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства— (22) Заявлено 30.10.72 (21) 1842359 26-9 с присоединением заявки №вЂ” (32) Приоритет—

Опубликовано 30.07.74. Бюллетень № 28

Дата опубликования описания 12.02.75 (51) М.Кл. Н 04Ь 3, 04

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621 394 42 (088.8) (72) Авторы изобретения

Г. А. Полиевский, А. М. Черныш и В. В. Болбат (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОКАНАЛА

ПЕРЕДАЧИ ДАННЫХ С ТРАНСФОРМАЦИЕЙ

СКОРОСТЕЙ МАНИПУЛЯЦИИ

Предмет изобретения

1

Изобретение относится к радиотехнике, в частности к системам передачи данных.

Известные устройства контроля для испытания цифровых систем связи не позволяют оценивать искажение характеристик в парцняльных подканалах радиогряктя переда tn дшшых с трансформацией скоростей манипуляции в области верхних и нижних частот, Цель изобретения — повышение точности разделения ошибок по их видам.

Эта цель достигается тем, что на передаче и приеме введены формирователь кода трансформации и формирователь чередования циклов сиги я лов.

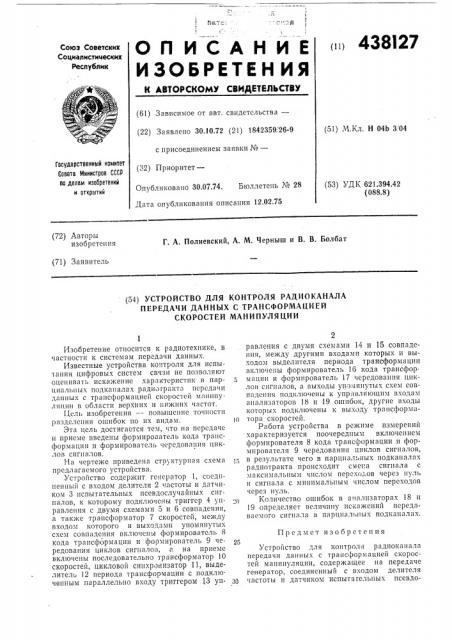

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит генератор 1, соединенный с входом делителя 2 частоты и датчиком 3 испытателbíûõ псевдослучайных сигналов, к которому подключены триггер 4 управления с двумя схемами 5 и 6 совпадения, я также трансформатор 7 скоростей, между входо I которого и выходямн упомянутых схем совпадения включены формирователь 8 кода трансформации и формирователь 9 чередования циклов сигналон, а на приеме включены последовательно трансформатор 10 скоростей, цикловой синхронизатор 11, выделитель 12 периода трансформации с подключенным параллельно входу триггером 13 уп2 равления с двумя схемами 14 и 15 совпадения, между другими входами которых и выходом выделителя периода трансформации включены формирователь 16 кода трансфор. мации и формирователь 17 чередования циклов сигналов, я выходы упомянутых схем совпадения подключены к управляющим входам анализаторов 18 и 19 ошибок, другие входы которых подключены к выходу трянсформяto тора скоростей.

Работа устройства в режиме измерений характеризуется поочередным включением формирователя 8 кода трансформации н формирователя 9 чередования пиклов сигналов, в результате чего в парциальных подканалах радиотракта происходит смена сигнала с максимальным числом переходов через нуль и сигнала с минимальным числом переходов через нуль. о Количество ошибок в анализаторах 18 н

19 определяет величину искажений передаваемого сигналя в пярциальных подканалах.

Устройство для контроля радиоканала передачи данных с трансформацией скоростей манипуляции, содержащее на передаче генератор, соединенный с входом делителя частоты и датчиком испытагельпых псевдо438127

П1 23ЙЯи(Й0 чпОЯь

П итнан чисть

Составитель А. Черныш

Техред 3. Тараненко

Редактор М. Бычкова

Корректор В, Кочкарева

Заказ 6377,Изд, № 1862 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-65, Раушская наб„д, 4/5

МОТ, Загорский цех случайных сигналов, и когорому подключены триггер управления с двумя схемами совпадения, а также трансформатор скоростей, а на приеме включены последовательно трансформатор скоростей, цикловой синхронизатор, выделитель периода трансформации с подключенным параллельно входу триггером управления с двумя схемами совпадения, а также два анализатора ошибок, подключенные к выходу трансформатора скоростей, отsu«aioiueeca тем, что, с целью повышения точности разделения ошибок по их видам, на передаче и приеме введены формиро4 ватель кода трансформации и формирователь чередования циклов сигналов, которые на передаче вкл1очены между входом трансформатора скоростей и выходами упомянутых

5 схем совпадения, входы которых соединены с выходом частоты, а на приеме включены между выходом выделителя периода трансформации и входами схем совпадения, причем инверсные входы триггера управления

10 подсоединены к выходам циклового синхронизатора, а выходы схем созпадения подключены к управляющим входам упомянутых анализаторов ошибок.