Устройство для поэлементного допускового контроля двухэлементных комплексных электрических цепей

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 438941

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 22.05.72 (21) 1784372/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 05.08.74. Бюллетень № 29

Дата опубликования описания 23.01.75 (51) М. Кл. G Olr 27,/ОО

Государственный комитет

Совета 1иинистров СССР оо делам иеооретений и открытий (53) УДК 621.317,791 (088.8) (72) Авторы изобретения А. И. Мартяшин, А, Е. Морозов, Б. Л. Свистунов и В. М. Шляндии

Пензенский политехнический институт (71) Заявитель! (54) УСТРОЙСТВО ДЛЯ ПОЭЛЕМЕНТНОГО ДОПУСКОВОГО

КОНТРОЛЯ ДВУХЭЛЕМЕНТНЫХ КОМПЛЕКСНЫХ

ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ

Изобретение относится к контрольно-измерительной технике.

Известно устройство для поэлементного допускового контроля двухэлементных комплексных электрических цепей, содержащее источник постоянного образцового напряжения, усилитель постоянного тока, в цепь отрицательной обратной связи которого включены параллельHо соединенные образцовые резистор и конденсатор; дифференциатор, вход которого подключен к выходу усилителя постоянного тока; две двухпороговые схемы сравнения, вход одной из которых соединен с выходом усилителя постоянного тока, а выходы обеих схем соединены со входом логической схемы; программный блок, управляющий источником постоянного напряжения и схемами сравнения.

Однако с помощью известного устройства невозможен поэлементный допусковый контроль двухэлементных LC-цепей.

С целью расширения функциональных возможностей в предлагаемое устройство введены ключ и линия задержки, управляемая от программного блока, причем выход этой линии задержки соединен с одним из входов ключа, другой вход которого подключен к выходу дифференциатора, а выход ключа соединен со входом второй схемы сравнения.

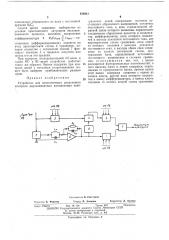

На чертеже приведена функциональная схема устройства в режиме контроля параметров параллельной 1.С-цепи.

Перед началом операции контроля по

5 команде программного блока ПБ в двухпороговых схемах 1 и 2 сравнения устанавливаются пороги срабатывания, соответствующие верхним и нижним граничным значениям контролируемых параметров. соответственно, L u

10 С, а в линии задержки 3 — время задержки открывания ключа 4. Затем ио команде

«пуск» напряжение амплитудой — Ео с источника постоянного образцового напряжения 5 подается через контролируемую цепь па вход

is усилителя постоянного тока (УПТ) G, в цепь отрицательной обратной связи которого включены параллельно соединенные образцовые резистор Яо и конденсатор Со.

В начальный момент времени с выхода

ЕО

УПТ 6 снимается напряжение С вЂ”, подаваес, мое на двухпороговую схему сравнения 1.

Если это напряжение превышает только один порог срабатывания, с выхода логической

25 схемы 7 дается сигнал «С в норме» (во всех остальных случаях — «брак по C»). Одновременно выходное напряжение УПТ 6 подается на вход дифференциатора 8, выходной сигнал которого представляет собой композицию иоЗО стоянного напряжения и напряжения, экспо438941

Предмет изобретения ат 76

Ре.зуЛ ma m Об iЛРОЛЯ

dm ПБ

Составитель Б. Свистунов

Техред Л. Акимова

Корректор Л. Орлова

Редактор Б. Федотов

Заказ 3706/16 Изд. № 134 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ненциально убывающего до нуля с постоянной времени RpCp, Спустя время задержки, выбираемое из условия практического затухания экспоненциального процесса, выходное напряжение

1 дифференциатора 8 ЛоЕосдиф (тдиф поL стояннная дифференцирования) подается на вход двухпороговой схемы 2 сравнения, которая совместно с логической схемой 7 фиксирует значение L в пределах допусков или выход его за эти пределы.

При контроле последовательной LC-цепи, а также RC- u RL-цепей устройство работает таким же образом. Время задержки при контроле цепей с активным сопротивлением может быть выбрано приблизительно равным нулю.

Устройство для поэлементного допускового контроля двухэлементных комплексных электрических цепей, содержащее источник постоянного образцового напряжения, усилитель постоянного тока, в цепь отрицательной обратной связи которого включены параллельно

5 соединенные образцовые резистор и конденсатор, дифференциатор, вход которого подключен к выходу усилителя постоянного тока, две двухпороговые схемы сравнения, вход одной из которых соединен с выходом усилителя

10 постоянного тока, а выходы обеих схем соединены со входом логической схемы, программный блок, управляющий источником постоянного напряжения и схемами сравнения, отличающееся тем, что, с целью

15 расширения функциональных возможностей, в него введены ключ и линия задержки, управляемая от программного блока, причем выход этой линии задержки соединен с одним из входов ключа, другой вход которого подклю20 чен к выхоу дифференциатора, а выход ключа соединен со входом второй схемы сравнения.