Входной дифференциальный каскад усилителя постоянного тока

Иллюстрации

Показать всеРеферат

"„г . знатен т .э--;-::,:, -;.к;..g

1 ш1 439855

ОП ИСА-Ни-Й

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистимеских

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 27.01.72 (21) 1742715/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 05.08.74. Бюллетень № 29

Дата опубликования описания 27,01.75 (51) 1. Кл. Ы 031 3д34

Государственный комитет

Совета Министров СССР

00 делам изобретений и открытий (53) УДК 621.375.432 (088.8) (72) Авторы

В. Н. Ьродовский, А. А. Замбржицкий и Ь. H. Каржавов

EIзО1 пстсп1!я (71) Заявитель (54) ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЪ|Й КАСКАД

УСИЛИТЕЛЯ ПОСТОЯННОГО ТОКА

Изобретение может быть использовано в автоматических системах управления.

Известен входной дифференциальный каскад усилителя постоянного тока, выполненный на четырех транзисторах, по два транзистора в каждодм плече, причем эмиттер входного транзистора соединен с базой выходного, эмиттеры выходных транзисторов объединены и через резистор соединены с минусовой шиной источника питания, а коллекторы выходных транзисторов соединены через резисторы с полосовой шиной источника питания.

Цель изобретения — уменьшение нулевого фона и дрейфа нуля усилителя постоянного пока — достигается тем, что в предлагаемом каскаде транзистора каждого плеча соединен с коллектором выходного транзистора другого плеча.

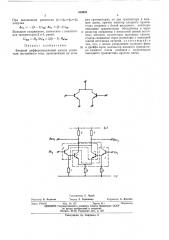

На чертеже приведена принципиальная схема устройства.

Входной дифференциальный каскад усилителя постоянного тока выполнен на четырех транзисторах 1 — 4 и резисторах 5 — 9. Первое плечо образовано транзисторами 1, 2, второе — транзисторами 3, 4, причем транзисторы

1 и 3 входные, а транзисторы 2 и 4 — выходные. Эмиттер транзистора 1 (3) соединен с базой транзистора 2 (4), эмиттеры транзисторов

2 и 4 объединены и через резистор 8 соединены с минусовой шиной источника питания.

Коллекторы транзисторов 2 и 4 соединены через резисторы 5 и 6 соответственно с плюсовой шиной источника питания, а коллектор транзистора 1 (3) каждого плеча соединен с коллектором транзистора 4 (2) другого плеча.

Сопротивления эмиттерных резисторов 7 — 9 выбирают такими, чтобы начальные токи всех транзисторов были одинаковы. Пусть на базу транзистора 1 подан сигнал такой полярности, что ток через него усиливается, а ток через транзистор 3 ослабевает. Величина изменения тока определяется коэффициентом усиления транзистора р и величиной тока входного сигнала

15 тВХ- 4, =- 11ДВХг — 4. == — -З4Х

Изменение тока в транзисторах 1 и 3 вызывает изменения токов в транзисторах 2 и 4:

ЬХй, — РВЬддЗ Р1Р21ВХг

20 Лг г 4 таг г 4 З ВХ

Ток, протекающий через резисторы нагрузки 5 и 6, также изменяется на величину Нд — т1 + т4 (д 1 1 3 г4) ВХг

25 тнд: тз+ т2: (З112 РЗ) гВХ.

Выходной сигнал, снимаемый с коллекторных резисторов 5 и 6, равен:

= Лтн, R, R„(P, — ВВВ4) <»

30 U22„Õ тНг Н R„(I 1)2,г 3) iÂÕ

439055 Предмет изобретения

8бПф

os>

Составитель Г. Челей

Техред 3. Тараненко

1(орректор А. Дзесова

Редактор Б. Федотов

Заказ 3704!16 Изд. № 127 Тираж 811 Подписчое

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д, 4/5

Типография, пр. Сапунова, 2

Прч выполнении равенства Р1= Рз= рз= р4 получим

Ai„, — () 1) г h,i„— (1)i,х„.

Выходное напряжение, снимаемое с коллекторов транзисторов.2 и 4, равно: вмк — ы 2 в — 2 () 1) в вы.

Входной дифференциальный каскад усилителя постоянного тока, выполненный на четырех транзисторах, по два транзистора в каждом плече, причем эмиттер входного транзистора соединен с базой выходного, эмиттеры выходных транзисторов объединены и через резистор соединены с минусовой шиной источника питания, коллекторы выходных транзисторов соединены через резисторы с плюсовой шиной источника питания, отли ч а ю1ци й."я тем, что, с целью уменьшения нулевого фона

l0 и дрейфа нуля, коллектор входного транзистора каждого плеча соединен с коллектором выходного транзистора другого плеча,