Устройство для преобразования десяти ных чисел в двоичные

Иллюстрации

Показать всеРеферат

» 43980l

ОПИСАНИЕ

ИЗОБРЕТЕН Ия

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) Заявлено 07.06,72 (21) 1795577/18-24 с присоединением заявки №вЂ” (32) Приоритет—

Опубликовано 15,08.74, Бюллетень № 30

Дата опубликования описания 10,04.75 (51) М.Кл. G 06f 5/02

Гасударственный комитет

Совета Министров СССР ао делам изооретейии и открытий (53) УДК 681.325.53 (088.8) (72) Авторы изобретения

И. Л. Андреев, И. Ф. Арский и В. А. Зарубин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДЕСЯТИЧНЫХ

ЧИСЕЛ В ДВОИЧНЫЕ

Изобретение относится к области вычислительной техники и предназначено для преобразования чисел из десятичной системы счисления в двоичную.

Известен преобразователь десятичного кода в двоичный, содержащий устройство ввода, десятичный регистр сдвига, счетчик десятичных разрядов с дешифратором, двоичный счетчик импульсов и схему управления.

Преобразование десятичного кода в двоичный в таком преобразователе осуществляется путем последовательного суммирования на счетчике значений двоичных эквивалентов десятичных разрядов, причем суммирование осуществляется последовательно не только для эквивалентов, но и для двоичных разрядов в эквиваленте.

Схема такого преобразователя сравнительно сложна.

Предложенное устройство для преобразования десятичных чисел в двоичные отличается тем, что содсржит блок формирования двоичных эквивалентов, входы которого соединены с выходами схемы запоминания десятичного числа, а выходы — со входами сумматора.

Усложнение рассматриваемого устройства с увеличением количества десятичных разрядов незначительно. Достаточно высокое быстродействие схемы достигается за счет преоб2 разования в двоичную форму всех десятичных разрядов одновременно и зависит не от размерности числа, а от значения цифр в его разрядах.

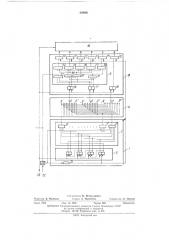

Схема предложенного устройства изображена на чертеже (для трех десятичных разрядов). В общем случае количество разрядов не ограничивается.

Распределитель импульсов 1 служит для

1ð управления процессом преобразования чисел и представляет собой микропрограммный автомат, состоящий из двоичного счетчика 2 и дешифратора 3.

Схема 4 запоминания десятичных чисел, подлежащих преобразованию в двоичный код, выполнена на переключателях 5 — 7. Клеммы переключателей, соответствующие одинаковым десятичным цифрам, запараллелены.

Блок 8 формирования двоичных эквивалентов предназначен для преобразования десятичных чисел в двоичные путем выделения на его выходах суммы разрядных единиц десятичного числа.

Блок 8 состоит из дешифратора 9, вентилей 10 — 15 и управляющих триггеров 16 — 18, предназначенных для фиксации временного интервала преобразования каждого десятичного разряда. Дешифратор 9 осуществляет непосредственное преобразование десятичных чиЗО сел в их двоичные эквиваленты.

43980!

Сумматор 19 (накаплива!о!цн!!) предназначен для сложения двоичных эквивалентов десятичных чисел.

Устройство содержит также схему «И» 20, элемент задержки 21, шипу 22 тактовых импульсов, шину 23 сигнала «11ачало преобразования». Дешифратор 9 выполнен на схемах

«ИЛИ» 24 — 28, «И» 29 — 31, «И-НЕ» 32, Перед преобразованием числа, вручную или автоматически от внешнего устроиства управления, I!0 шине 23 подается сигнал

<>. Этим спгпалоh! устанавливаются в «О» триггеры с1!с и!ка 2 и сумматора 19, а управляющие триггеры

16 — 18 блока 8 формирования двоич ых эквивалентов — в «1».

Тактовые импульсы при этом через схему

«И» 20 и вентили дешифратора 3 проходят на клеммы переключателей 5 — 7. Первый тактовый импульс через соответствующий вентиль, связанный с нулевой шиной переключателей, устанавливает в «О» управля!ощий триггер, если на соответствующем переключателе его выставлена цифра «О». Этим исключается учет данного разряда в суммарном двоичном эквиваленте, подаваемом на сумматор 19.

Задержанный элементом задержки 21 первый импульс, поступает, во-первых, на вход счетчика 2, меняя его состояние и подготавливая прохождение второго тактового импульса со схемы «И» 20 через следующий вентиль; во-вторых, приходит на вход вентилей 10 — 15 и «переписывает» двоичный эквивалент десятичных цифр, выделяемый блоком 8 формирования двоичных эквивалентов, в соответствии с состоянием управляющих триггеров 16 — 18 на сумматор 19.

Второй тактовый импульс через вентиль дешифратора 3 поступает на клеммы переключателей 5 — 7, соответствующие цифре «1», и исключает очередную декаду из рассмотрения, если «1» фиксировалась каким-либо из переключателей. Связанный с этим переключателем триггер устанавливается в «О» и в соот4 ветствии с вновь установившейся комбинацией на триггерах 16 — 18 и дешифраторе 9 вторым, задержанным на элементе 21 импульсом, к содержимому сумматора 19 прибавляется очередной двоичпыи эквивалент. На сумматоре, таким образом, накапливается сумма.

Операция суммирования двоичных эквивалентов десятичных разрядов продолжается до тех пор, пока все управляющие триггеры не

ip установятся в «0», т. е. пока не закончится преобразование десятичных цифр во всех разрядах.

Максимальное количество импульсов преобразования равно десяти. Сдвиг импульсов, поступающих на вход псрекл!очателей, осуществляется счетчиком 2 и дешифратором 3.

Из возможных шестнадцати комбинаций счетчика используется только 10. В начальное состояние счетчик возвращается сигналом

«Начало преобразования».

Суммарные двоичные эквиваленты выделяются схемами «И» 29 — 31, «ИЛИ» 24 — 28 и меня)от свое значение при переходе любого из управляющих триггеров 16 — 18 из первона чального состояния «1» в состояние «О».

Когда все управляющие триггеры установятся в «0», схема «И-НЕ» 32 выдает сигнал

«Конец преобразования», который запрещает дальнейшее прохождение тактовых импуль сов через схему «И» 20.

Предмет изобретения

Устройство для преобразования десятичных чисел в двоичные, содержащее распределитель, выходы которого соединены со входами схемы запоминания десятичного числа, и сумматор, от,!ичающееея тем, что, с целью упрощения устройства, оно содержит блок формирования двоичных эквивалентов, входы которого соединены с выходами схемы запоминания десятичного числа, а выходы соединены со входами сумматора.

439801

25 ZZ

Составитель В. Игнатущснко

Текред 3. Тараненко

Редактор Б. Нанкнна

Корректор Л, Орлова

Подписное

МОТ, Загорский цек

Заказ 7523 11зд.. и 1918 Тираж 624

ЦНИИ11И Государственного комитета Совета Министров СССР по делам изобретений It открытий

Москва, Ж-35, Раушская наб., д. 4/5