Двойной балансный модулятор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистицеских

Республик

" 439895 (61) Зависимое от авт. свидетельства— (51) М.Кл. Н 03с 1l54 (22) Заявлено 23.07.70 (21) 1462790/26-9 с присоединением заявки ¹â€” (32) Приоритет—

Опубликовано 15.08.74. Бюллетень № 30

Дата опубликования описания 19.05.75

Государственныи комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК 621.376. .22(088.8) (72) Автор изобретения

Г. М. Микиртичан

Центральный научно-исследовательский институт связи (71) Заявитель

Изобретение относится к модуляторам и может быть использовано в устройствах амплитудной и фазовой модуляции, устройствах перемножения сигналов и других радиотехнических устройствах.

Известен двойной балансный модулятор, содержащий фазоинверсный каскад на транзисторе, охваченный параллельной обратной связью, вход которого соединен с источником сигнала, и электронный ключ, управляемый 10 источником несущей частоты.

Недостатками известного балансного модулятора являются плохое подавление несущей частоты и отсутствие подавления модулирующего сигнала. 15

Для улучшения подавления несущей частоты и модулирующего сигнала в предлагаемый модулятор в цепь эмиттера транзистора фазоинверсного каскада введены последовательно соединенные резисторы, параллельно 20 одному из которых включен электронный ключ.

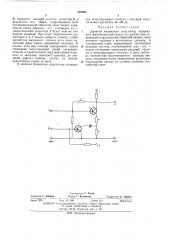

На чертеже показана принципиальная схема описываемого модулятора, содержащего фазоинверсный каскад на транзисторе 1, ох- 25 ваченный параллельной обратной связью посредством резистора 2, вход которого через клемму 3 соединен с источником сигнала, два последовательно соединенных резистора 4 и 5 в цепи эмиттера транзистора этого каскада, и 30 выходную клемму 6. Параллельно резистору 5 включен электронный ключ на транзисторе 7, база которого через клемму 8 подключена к источнику несущей частоты.

Модулятор работает следующим образом.

Сигнал с входной клеммы 3 поступает на выходную клемму 6 через фазоинверсный каскад на транзисторе 1 и через резистор 2 параллельной обратной связи. Эти сигналы на выходной клемме 6 (первый по отношению ко второму) имеют фазовый сдвиг 180, так как транзистор 1 включен по схеме с общим эмиттером. В обычном усилительном режиме, когда сумма сопротивлений резисторов 4 и 5 значительно меньше сопротивления резистора 2, преобладает сигнал в цепи коллектора транзистора 1.

При увеличении суммы сопротивлений вышеуказанных резисторов до значения сопротивления резистора 2 сигнал в цепи коллектора и сигнал, поступающий на выход через резистор 2, будут иметь одинаковую амплитуду и противоположную фазу, и суммарный сигнал на выходе будет равен нулю.

При дальнейшем увеличении суммы сопротивлений резисторов 4 и 5 на выходе будет преобладать сигнал, прошедший через резистор 2 цепи параллельной обратной связи.

Транзистор 7 электронного ключа замыкает в такт с приходящим на его вход (клемму

439895

Составитель Г. Челей

Текред Г. Васильева

Редактор С. Хейфиц

1(орректор О. Тюрина

Заказ 7573 Изд. Х 1924 Тираж 811 Подписное

ЦНИИГ1И Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская паб., д. 4/5

МОТ, Загорский филиал

8) сигналом несущей частоты резистор 5, в результате чего общее сопротивление цепи последовательной обратной связи может изменяться таким образом, что отношение его к сопротивлению резистора 2 будет меньше или больше единицы. При этом сопротивления резисторов 4 и 5 можно выбрать такими, чтобы амплитуда выходного сигнала до и после изменения фазы имела одинаковое значение. В случае, если при помощи электронного ключа отношение сопротивлений цепей последовательной и параллельной обратной связей изменять от значения, меньшего единицы, до зна чения, равного единице, сигнал на выходе практически упадет до нуля.

В двойном балансном модуляторе подавле4 ние модулирующего сигнала и несущей частоты может достигать 40 — 60 дб.

Предмет изобретения

5 Двойной бала нсный модулятор, содержащий фазоинверсный каскад на транзисторе, охваченный параллельной обратной связью, вход которого соединен с источником сигнала, и электронный ключ, управляемый источником

10 несущей частоты, отличающийся тем, что, с целью улучшения подавления несущей частоты и модулирующего сигнала, в цепь эмиттера транзистора фазоинверсного каскада введены последовательно соединенные резисторы, 15 параллельно одному из которых включен упомянутый ключ.