Устройство для формирования импульсных последовательностей

Иллюстрации

Показать всеРеферат

»1439909

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских.Социалистических

Республик (61) Зависимое от авт. свидетельства 224566 (22) Заявлено 22.09.69 (21) 1361719/26-9 (51) М.Кл. Н 03k 3/78

H 03k 3/64 с ирисоединсиием заявки ¹â€”

-Государственный комитет

Совета Министров СССР па делам изобретений и открытий (32) Приоритет—

Опубликовано 15.08.74. Бюллетень № 30 (53) УДЫ 621.373.444 (088.8) Дата опубликования описания 21.03.75 (72) Автор изобрете гия

А, П. Земляков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретение относится к радиотехнике и мо>кет быть использовано в радионавигации, радиолокации, измерительной технике.

Известное устройство для формирования импульсных последовательностей по авт. св. .М 224566 имеет низкую точность формирования, а к блоку управления устройства предьявляются высокие требования.

Для повышения точности формирования и сии>кения требований к быстродействию блока управ.пения, в предлагаемом устройстве между выходом установки нуля делителя частоты и выходом устройства введен формирователь импульсов сброса, присоединенный управляющим входом к одному из выходов блока управления, содержащий, например, схему совпадения, подключенную выходом ко входу установки нуля делителя частоты, первым входом — к выходу устройства, а вторым входом — к выходу триггера, один вход которого соединен с программным блоком, а второй— через элемент задержки с выходом схемы совпадения.

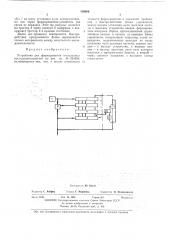

На чертеже приведена функциональная схема описываемого устройства, содержащего высокочастотный генератор 1, делитель 2 частоты, схему совпадения 8, регистр 4, программный блок 5, схему 6 уточнения, логическую схему «И» 7, триггер 8, элемент 9 залер>кки.

Устройство работает следующим образом.

При поступлении сигнала генератора 1 на вход делителя 2 частоты число в делителе возрастает. Код этого числа поступает иа схему совпадения 8 кодов. Сюда поступает также код числа, записанного в статический регистр 4 из программного блока 5. В момент равенства этих чисел схема совпадения 8 формирует сигнал, поступающий через схему б уточнения или непосредственно на выход устройства и одновременно в программный блок 5 и иа логическую схему «И» 7. Из программного блока 5 в статический регистр 4 записывается новое число, соответствующее времен15 ному положеншо следующего формируемого импульса, при этом на триггер 8, управпяющий схемой «И» 7, сигнал не подается (или подается сигнал, подтверждающий нулевое поло>кение триггера 8), триггер 8 находится в

20 состоянии «О», схема «И» 7 закрыта.

После формирования последнего сигнала из программного блока в статический регистр 4 записывается число, соответствующее моменту окончания очередного цикла формируемой по25 следовательности, одновременно подается сигнал на триггер 8, который переходит в состояние «1». С триггера 8 подается единичный сигнал на схему «И»?.

При формировании импульса схемой совпадения 3 кодов сигнал поступает через схему

439909

Предмет изобретения

Составитель Ю. Еркин

Тсхред T. Миронова

Редактор С. Хейфиц

Корректор И. Позияковскаи

Заказ 6539, Изд. ¹ 1900 Тираж,811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам. изобретений и открытий

Москва, jI(35, Раушская иао., д. 4/5

Обл. тип. 1(сстромского управления издательств, полиграфи и книжной торговли

«П» 7 на шину установки нуля иеносрсдственно или через формирователь-усилитель (на схеме не показан). Этот же импульс подается иа триггер 8 через элемент 9 задержки и возвращает триггер 8 в нулевое состояние.

Далее все процессы повторяются. Быстродействие программного блока определяется только интервалами между импульсами последовательности.

Устройство для формирования импульсных последовательностей по авт. св. ¹ 2245бб, отличающееся тем, что, с целью повышения точности формирования и снижения требования к быстродействгио блока управления, между входом уста1ювки нуля делителя частоты и выходом устройства введен формнрова5 тель импульса сброса, присоединенный управляющим входом к одному из выходов блока управления, содержащии, например, схему совпадения, подключенную выходом ко входу установки нуля делителя частоты, первым вхо10 дом — к выходу устройства, а вторым входом — к выходу три гера, один вход которого соединен с программным блоком, а второй— через элемент задержки с выходом схемы совпадения.