Устройство для синхронизации импульсов

Иллюстрации

Показать всеРеферат

Союз Советских »4399И

С ц влнстнческнх

Республик

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) Заявлено 24.11.72 (21) 1849468/26-9 с присоединением заявки №вЂ” (32) Приоритет—

Опубликовано 15.08.74. Бюллетень ¹ 30

Дата опубликования описания 21.03.75 (51) М.Кл. Н 03k 5/13 еосударстеенный комнтет

Совета Мнннстрее СССР

А0 делам нзабретеннй н открытии (53) УДК 681.142.67 (088.8) (72) Авторы ,изобретения

Э. О. Вольфовский, И. И. Трофимов и И. К. Хомяков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в электронных цифровых вычислительных машинах, цифровых измерительных приборах и цифровых преобразователях.

Известно устройство для синхронизации импульсов, содер>кащее входной триггер, шину синхроимпульсов, шину асинхронных импульсов, три схемы «И» и две схемы «НЕ», причем шина спнхроимпульсов подключена к одному из входов третьей схемы «И» и через два последовательно включенных инвертора к другому входу третьей схемы «И», а один из выходов входного триггера соединен с одним из входов первой схемы «И».

Недостаток такого -устройства заключается в том, что в исходном состоянии при отсутствии асинхронных импульсов иа втором входе третьей схемы «И» поддер>кивается разрешающий сигнал, который вследствие инерционности элементов сохраняется в течение некоторого интервала времени после того, как на втором входе второй схемы «И» и на первом входе третьей схемы «И» появляется очередной сиихронизирующий импульс. Это приводит к появлеишо ложного сигнала иа выходе устройства, что сии>кает надежность в его работе.

Для повышения надежности в предлагаемое устройство введены триггер и схема «НЕ».

Шина асинхронных импульсов подключена ко входу введенной схемы «НЕ», выход которой соединен с первым входом входного триггера и вторым входом первой схемы «И». Выход первой схемы «И» подключен к первому входу введенного триггера, выход которого через третью схему «И» соединен со вторым входом входного триггера. Второй выход входного триггера подключен через вторую схему «И» ко второму входу введенного триггера, а выход первого инвертора соединен с третьим входом первой схемы «И» и вторым входом второй схемы «И».

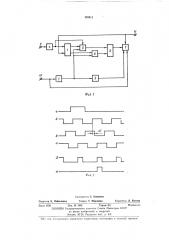

На фиг. 1 представлена функциональная схема описываемого устройства: на фиг. 2— временная диаграмма, иллюстрирующая формирование выходного импульса.

Устройство содержит входной триггер 1, три схемы «НЕ» 2 — 4, три схемы «И» 5 — 7 и дополнительный триггер 8. Единичный выход

20 триггера 1 соединен с первым входом схемы

«И» 5. Шина 9 входных асинхронных импульсов через дополнительную схему «НЕ» 4 соединена с единичным входом триггера 1 и вторым входом схемы «И» 5, выход которой под25 ключеи к единичному входу триггера 8. Нулевой выход триггера 1 соединен с первым входом схемы «И» 6, выход которой подключен к нулевому входу триггера 8. Шина 10 синхроиизирующих импульсов подключена к перво30 му входу схемы «И» 7 и ко входу схемы «НЕ>.

439911

2, выход которой соединен с третьим входом схемы «И» 5, вторым входом схемы «И» б и со входом схемы «НЕ» 8. Выход схемы «НЕ> 8 подключен ко второму входу схемы «И» 7, третий вход которой соединен с единичным выходом триггера 8, а выход схемы «И» 7— с нулевым входом триггера 1 и выходной шиной 11 устройства.

Устройство работает следующим образом.

Входной асинхронный импульс (см. фпг. 2, а) поступающий на шину 9 устройства, устанавливает триггер 1 в состояние «1». При этом с единичного выхода триггера 1 на первый вход схемы «И» 5 поступает разрешающий сигнал, а с нулевого выход на первый вход схемы

«И» б — запрещающий сигнал. В течение промежутка времени, равного длительности входного импульса, »а второй вход схемы «И» 5 подается запрещающий сигнал с выхода схемы «НЕ» 4. По истечении этого времени спгEIBJI на втором входе схемы «И» 5 становится также разрешающим. В паузах между спнхронизирующими импульсами, поступающими на шину 10 устройства (см. фпг. 2, б), на выходе схемы 2 «НЕ» формируются сигналы (см. фиг. 2, в), поступающие на третий вход схемы

«И» 5 и второй вход схемы «И» б. При совпадении разрешающих сигналов па нервом, второй и третьем входах схемы 5 на выходе этой схемы формируется импульс, который устанавливает триггер 8 в состояние «1». С единичного выхода триггера 8 на третий вход схемы

«И» 7 поступает разрешающий сигнал. На выходе схемы 7 формируется сигнал при появлении на ее остальных входах синхронизирующего сигнала с шины 10 и синхронизирующего сигнала после двойной инверсии с выхода схемы «НЕ» 3 (см. фиг. 2, г), Очередной синхронизирующий импульс проходит на шипу 11 устройства (см. фиг. 2, е) и нулевой вход триггера l. Вследствие задержки в схеме «HF» 2 сигнал на ее выходе (см. фиг. 2, в) остается разрешающим в течение некоторого интервала времени Лт, когда на шину 10 устройства подается очередной разрешающий сигнал (см. фиг. 2, б). Так как, кроме входного синхронизирующего сигнала, на второй вход схемы «И»

7 поступает сигнал с выхода схемы «НЕ» 8 (см. фиг. 2, г), то результирующий разрешающий сигнал, действующий на первом и втором входах схемы 7 (см. фиг. 2, д) не перекрывается во времени с разрешающим сигналом, формируемым на выходе схемы «НЕ» 2 (см. фиг.

2, в). После установки триггера 1 в состояние

ip «О» на вход схемы «И» б подается разрешающий сигнал с нулевого выхода этого триггера.

Очередной разрешающий сигнал с выхода схемы «НЕ» 2 проходит в паузе между синхронизпрующими импульсами через схему б на ну15 левой вход триггера 8 и устанавливает его в состояние «О». Схема устройства возвращается в исходное состояние.

Предмет изобретения

Устройство для синхронизации импульсов, содержащее входной триггер, шину синхропмпульсов, шину асинхронных импульсов, три схемы «И» и две схемы «НЕ», причем шина

25 спнхроимпульсов подключена к одному из входов третьей схемы «И» и через два последовательно включенных инвертора к другому входу третьей схемы «И», а один из выходов ходного триггера соединен с одним из входов первой схемы «И», отличающееся тем, что, с целью повышения надежности, в него введены триггер и схема «НЕ», причем шина асинхронных импульсов подключена ко входу введенной схемы «НЕ», выход которой соединен с первым входом входного триггера и вторым входом первой схемы «И», выход которой подключен к первому входу введенного триггера, выход которого через третью схему «Й» соеди. нен со вторым входом входного триггера, вто о рой выход входного триггера подключен через вторую схему «И» ко второму входу введенного триггера, а выход первого инвертора соединен с третьим входом первой схемы «И» и вторым входом второй схемы «И».

139911 фиг. 1.е

РиГ. с

Составитель F.. Ковалева

Техред T. Миронова

Редактор А, Г1ейсоченко

Корректор Л. Котова

Обл. тип. Костромского управления издательств, полиграфии п книжной торговли.Заказ 6539 Изд. № 1900 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 5К-З5, Раушская наб., д. 4/5