Аналого-цифровой преобразователь с коррекцией динамических погрешностей

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) 3 а виси мое от а вт. свидетельств я†(22) Заявлено 11.09,72 (21) 1827584/26-9 с присоединением заявки №вЂ” (32) Приоритет—

Опубликовано 15.08.74. Бюллетсиь М 30

Дата опубликования описания 21.03.75

« 4399)3

Союз Советских

Социалистических

Реслублик (51) МКл. Н 031 13/17

1 асударствеиив и комитет

Совета й1ииистрае СССР оо делеи изабретеинй и открытии (53) УДК 681.325 (088.8) (72) Авторы изобретения

Б. Г. Вальский, Г. Г. Живилов и В. В. Островерхов (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

С КОРРЕКЦИЕЙ ДИНАМИЧЕСКИХ ПОГРЕШНОСТЕЙ

Изобретение относится к области электроизмерительной и вычислительной техники и может быть использовано для преобразования быстроизменяющихся во времени непрерывных сигналов в цифровой код.

Известен аналого-цифровой преобразователь с коррекцией динамических погрешностей, содер>кащий сравнивающие устройства, преобразователь кода в иапря>кение, блок контрольных напряжений, схемы суммирования напряжений, логические схемы, генератор импульсов и распределитель тактовых им-. пульсов.

Однако в известном устройстве в момент, когда время переноса единиц в регистре триггеров разрядов соизмеримо с длительностью такта, не обеспечивается максимально возможное быстродействие, так как в этом случае необходимо учитывать время, нужное для изменения состояния триггеров разрядов регистра основного преобразователя кода в напряжение ири коррекции дшгамических погрешностей.

С целью увеличения быстродействия в предлагае»ое устройство дополнительно введен преобразователь кода в напряжение, аналоговый выход которого подключен к схеме суммирования компенсирующих напряжений, а цифровой выход соединен со входом цифрового сумматора, иа другой вход которого подключен цифровой выход основного преобразователя кода в напря>кение.

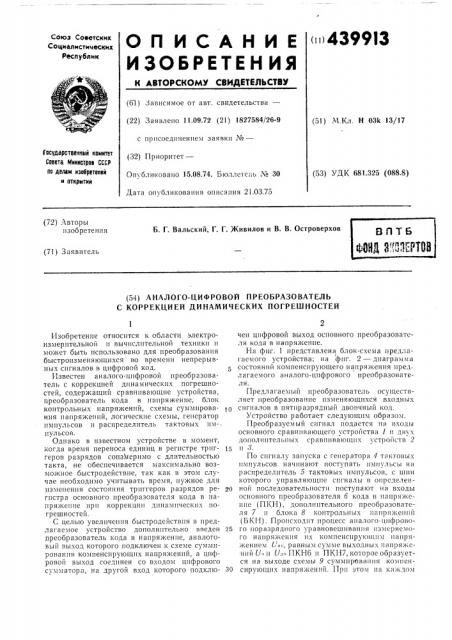

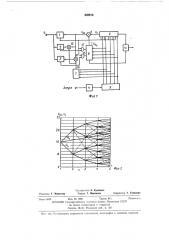

На фиг. 1 представлена блок-схема предлагаемого устройства; иа фиг. 2 — диаграмма состояний компенсирующего напря>кения предлагаемого аналого-цифрового преобразователя.

Предлагаемый преобразователь осугцествляет преобразование изменяющихся входных сигналов в пятиразрядный двоичный код.

Устройство работает следующим образом.

Преобразуемый сигнал подается ня входы основного сравнивающего устройства 1 и днуi дополнительных сравииваюгцих устройств 2

15 и 3.

По сигналу запуска с генератора 4 тактовых импульсов начинают поступать импульсы ня распределитель 5 тактовых импульсов, с шии. которого управляющие сигналы в определенно ной последовательности поступают на входы основного преобразователя 6 кода в напряжение (ПКН), дополнительного преобразователя 7 и блока 8 контрольных напряжений (БКН). Происходит процесс аналого-цифрово25 го поразрядного уравновешивания измеряемого напряжения их компенсирующим напряжением U. равным сумме выходных ианря>ксний U» U ПКНб и ПКН7, которое образуется на выходе схемы 9 суммирования комиен30 сирующих напряжений. При этом иа каждом

439913!

-ом такте на второй вход дополнительного сравнивающего устройства 2 и аналогичного сумматора 10 поступает компенсиру!ощее напряжение

Uoi; (i) и контрольные напряжение U; (! ), а на второй вход сравнивающего устройства 8 с аналогового вычитателя 11 поступает разность этих напряжений. Основной преобразователь 6 кода в напряжение работает как обычный

ПКН в аналого-цифровом преобразователе поразрядного уравновешивания, вырабатывая 10 напря>кения У. разрядов.

Блок 8 контрольных напряжений независимо от работы сравнивающих устройств на каждом такте преобразования последовательно выдает контрольное напряжение U„(i) 2). Дополни- 1й тельный преобразователь 7 кода в напряжение вырабатывает компенсационное напря>кение положительной илп отрицательной полярности, равное U;.(i)2) =,4=Уд.; .2, когда имеются соответствующие команды со сравни- 20 вающих устройств.

Процесс уравновешивания измеряемого напря>кения компенсирующим при Up. — U:«â€”

=U к,„...- может быть записан следующим образом > 5

Л

U.;;(!.=Л ) =Un,„,„;,- (Ха! .2 -+Zn;„.2 ), где

>=я — ) (+1 прп f U,. (i) f ) f Уо(е)+Удо (i — 1) i

О при i U,- (i) ) (i U (i) +У,-„, (i — 1) ЗО

+1 при /U,-(i) ) U (i)+У; (i — 1)—

+U (i) f

0 при (Uo(i) +Uao(i — 1)+U;(!) ) > U(i) ) > (U(i)+U. (! 1)— — U,(!)ф — 1 при (U,(i) )((U (!)+

+Удо(! — 1) — U (i) !.

Здесь а; =+1, когда на,i-ом такте срабатывает сравнивающее устройство 1; 40 а =+1, когда срабатывают сравнивающие устройства 1 п 2 и с выхода схемы совпадений

12 поступает сигнал на сложение Удо (i), а! = — 1, когда не срабатывают сравнивающие устройства 1 и 8, и с выхода инверсной 45 схемы совпадений И поступает сигнал на вычитание Удо(i), При преобразовании постоянного напря>кения U (фиг. 2) процесс уравновешивания происходит в обычном аналого-цифровом преобразователе поразрядного уравновешивания.

В этом случае работает только преобразователь 6 кода в напряжение, а дополнительный преобразователь 7 не выдает напря>кение на схему 9 суммирования.

В случае кодирования линейно-изменяющегося напряжения U..-z величина и направление компенсирующего напряжения У. изменяются (на фпг. 2 показан пунктирнымп линиями) таким образом, чтобы можно было следить в процессе преобразования за изменением входного напряжения. При этом работают оба преобразователя 6 и 7 кода в напряжение, а сумма их кодов, образуемая на цифровом сумматорс 14, соответствует к концу цикла преобразователя кодовому эквивалейту преобразуюп(его !!апр51жснпя.

Динамическая ошибка при этом, равная разности Л: = U. . (! = V) — У (1=Ц, либо пол иост>яо корректируется (при малых скоростях изменения входного сигнала), либо значительно уменьшается (Ill>!1 больших скоростях изменения входного сигнала).

В предлагаемом преобразователе не производится перенос ед!!нпц в регистре триггеров разрядов преобразователя 6 кода в напряжение, а следовательно, время преобразования определяется выражением т„„=!v (l,!, +i,,:,) где Л вЂ” число разрядов преобразователя;

t,ð — время, необходимое а проведение операции сравнения;

/,;, — время, необходимое на переключение компенсирующего напряжения в преобразователе кода в напря>кение.

Предмет изобретения

Лиалого-цифровой преобразователь с коррекцией динамических погрешностей. содержащий сравнивающие устройства, преобразователь кода в напря>кение, блок контрольных напряжений, схемы суммирования напряжений, логические схемы, генератор импульсов и распределитель тактовых импульсов, отли-! ающийся тем, что, с целью увеличения быстродействия, в него дополнительно введен преобразователь кода в напряжение, аналоговый выход которого подключен к схеме суммирования компенсирующих напря>кений, а цифровой выход соединен с входом цифрового сумматора, на другой вход которого подключен цифровой выход основного преобразователя кода в напряжение.

439913

Фиг 1

Составитель А. Кузнецов

Техред Т. Миронова

Корректор T. Гревцова

Редактор Т. Морозова

Подписное

Заказ 6539

Изд. № 1900 Тираж 811

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Обл. тип. Ко:тромского управления издательств, полиграфии и книжной торговли