Селектор для импульсных асинхронных системсвязи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

tttt 439929

Союз Советских

Социалистических

Республик (б1) Зависимое от авт. свидетельства (22) Заявлено 06.03.72 (21) 1755796/26-9 с присоединением заявки (32) Приоритет

Опубликовано 15.08.74. Бюллетень № 30

Дата опубликования описания 29.01.75 (51) М. Кл, Н 04b 1/10 государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.396.49 (088.8) "ъ ° 1 Ь

ФЙД 3 М РК (72) Автор изобретения

О. Г. Каратаев

171) Заявитель (54) СЕЛЕКТОР ДЛЯ ИМПУЛЪСНЫХ АСИНХРОННЫХ СИСТЕМ

СВЯЗИ

Изобретение относится к области передачи сигналов, а именно, к селекторам для импульсных асинхронных систем связи.

Известен селектор для импульсных асинхронных систем связи с время-импульсной модуляцией, содержащий линию задержки с отводами, подсоединенными к соответствующим входам схемы совпадения, фиксирующей адресную группу, интегратор, линию задержки с величиной задержки несколько больше максимально возможной длительности импульса совпадения и фантастрон, выход которого является выходом селектора.

Это устройство малоэффективно, поскольку импульсы адреса, поступающие на вход селектора, имеют разную амплитуду, что влияет на положение во времени декодированных имII) ËÜÑ0Â.

С целью уменьшения влияния амплитудных изменений входных импульсов на положение во времени декодированных импульсов выход схемы совпадения, фиксирующей адресную группу, одновременно подключен через вход и выход линии задержки с величиной задержки, несколько больше максимально возможной длительности импульса совпадения, к первому входу фантастрона, а через первый вход,и выход интегратора — ко второму входу фантастрона, выход которого подсоединен ко второму входу интегратора.

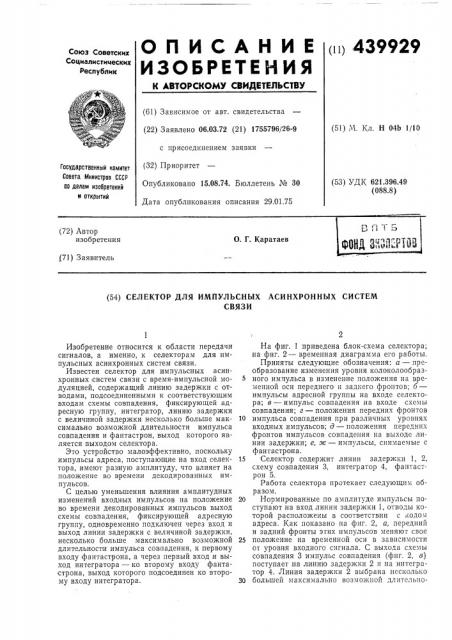

На фиг. 1 приведена блок-схема селектора; на фиг. 2 — временная диаграмма его работы.

Приняты следующие обозначения: а — преобразование изменения уровня колоколообразного импульса в изменение положения на временной оси переднего и заднего фронтов; б— импульсы адресной группы на входе селектора; в — импульс совпадения на входе схемы совпадения; г — положения передних фронтов

10 импульса совпадения при различных уровнях входных импульсов; д — положения передних фронтов импульсов совпадения на выходе линии задержки; е, яс — импульсы, снимаемые с фантастрона.

15 Селектор содержит линии задержки 1, 2, схему совпадения 3, интегратор 4, фантастрон 5.

Работа селектора протекает следующим образом.

20 Нормированные по амплитуде импульсы поступают на вход линии задержки 1, отводы которой расположены в соответствии с кодом адреса, Как показано на фиг. 2, а, передний и задний фронты этих импульсов меняют свое

25 положение на временной оси в зависимости от уровня входного сигнала. С выхода схемы совпадения 3 импульс совпадения (фиг. 2, в) поступает на линию задержки 2 и на интегратор 4. Линия задержки 2 выбрана несколько

30 большей максимально возможной длительно439929 сти импульса совпадения. Напряжение на выходе интегратора 4 в момент окончания импульса совпадения прямо пропорционально его длительности, Этим напряжением управляется фантострон 5 таким образом, что длительность формируемого им импульса равна половине длительности импульса совпадения.

Фантострон 5 запускается передним фронтом импульса совпадения, прошедшего через линию задержки 2. Таким образом, фаптастрон

5 кончает генерировать импульс в один и тот же момент времени (фиг. 2, д, е, ж), независимо от уровня импульсов на входе селектора (фиг. 2, а).

Предмет изобретения

Селектор для импульсных асинхронных систем связи с время-импульсной модуляцией, содержащий линию задержки с отводами, подсоединенными к соответствующим входам схемы совпадения, фиксирующей адресную группу, интегратор, линию задержки с величиной задержки несколько больше максимально воз5 можной длительности импульса совпадения и фантастрон, выход которого является выходом селектора, отличающийся тем, что, с целью уменьшения влияния амплитудных изменений входных импульсов на положение во

10 времени декодированных импульсов, выход схемы совпадения, фиксирующей адресную группу, одновременно подключен через вход и выход упомянутой линии задержки с величиной задержки, несколько больше максимально

15 возможной длительности импульса совпадения, к первому входу фантастрона, а через первый вход и выход интегратора — ко второму входу фантастрона, выход которого подсоединен ко второму входу интегратора.

439929

I т

Фиг г

Составитель Н. Герасимова

Редактор Л. Цветкова

Техред Т. Миронова Корректор А. Дзесова

Заказ 3718/10 Изд. № 1897 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Рэушская наб., д. 4/5

Типография, пр. Сапунова, 2