Устройство для синхронизации по циклам

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 439936

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 24.10.72 (21) 1840490/18-24 с присоединением заявки № (32) Приоритет (51) М. Кл. H 04l 7/08

G 08с 25/00

Гооударствеииый комитет

Совета Министров СССР па делам изобретений и открытий

Опубликовано 15.08.74. Бюллетень № 30 (53) УДК 621.394.662.2 (088.8) Дата опубликования описания 29.01.75 (72) Авторы изобретения С. А. Даниэлян, М. Н. Колтунов, Г. В. Коновалов, Ю. М. Супер и В. И. Ячевский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ

Изобретение относится к технике передачи дискретных сообщеиий в условиях воздействия сильных:импульсных помех. Применение устройства особенно целесообразно при использовании методов, основанных на передаче дешифрируемой на приеме синхрогруппы (маркерной группы) в случае довольно большой вероятности сбоя при ее дешифрации.

Известны устройства цикловой синхронизации, осуществляющие параллельный поиск синхрогруппы на всех позициях цикла. Однако существенным недостатком эIHx устройств является их большая аппаратурная сложность.

Известные устройства цикловой синхронизации, реализующие последовательный поиск синхрогруппы и работающие в условиях:интенсивных импульсных помех, как правило, не обеспечивают высокой помехоустойчивости, особенно в переходном режиме.

Целью изобретения является повышение помехоустойчивости B переходном и в установившемся режимах устройством цикловой синхронизации, работающим по принципу последовательного поиска синхрогрупп.

Сущность изобретения заключается в том, что в устройстве первый выход блока анализа, соединенный с первыми входами двух схем

«И», и второй выход блока анализа подключены соответственно к первому и второму входам блока определения сбоев, управляющий вход которого соединен с выходом дешифратора нулевого состояния. Третий вход блока оп,ределения сбоев соединен с выходом управляемого делителя и входом блока анализа. Первый и вгорой выходы блока определения сбоев подключены соответственно ко второму входу управляемого делителя и ко входу обратного счета, реверсивного счетчика. Вторые входы схем «И» подключены соответственно к перво1О му и второму выходам тр итера индикации.

Выходы схем «И» соединены соответственно со входом установки и входом прямого счета реверсивного счетчика.

В устройстве блок определения сбоев выполнен с применением схем «И», «ИЛИ», «НЕ» и триггера. Первый вход триггера подключен через схему «ИЛИ» к первому входу блока. Второй вход схемы «ИЛИ» соединен со вторым выходом блока и выходом первой схемы «И».

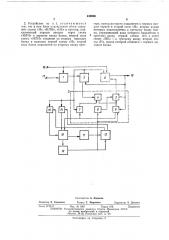

20 Второй вход блока подключен ко второму входу триггера, выход которого подключен к первым входам первой и второй схем «И», вторые входы которых подсоединены к третьему входу блока, управляющий вход которого под25 ключен к третьему входу первой схемы «И» и через схему «HE» — к третьему входу второй схемы «И», выход которой соединен с первым выходом блока, На чертеже представлена схема устройства.

30 Предлагаемое устройство содержит дешиф439936

15 го г5

3О

65 ратор 1 синхрогруппы, блок 2 анализа, блок определения сбоев 3, содержащий триггер 4, схемы «И» 5,и 6, схему «ИЛИ» 7, схему «HF»

8, управляемый делитель 9, реверсивный счетчик 10, дешифраторы 11 и 12 заданного и нулевого состояний, триггер индикации 13, схемы «И» 14 и 15, входы 16 и 17 и выход 18 устройства.

На входы дешифратора синхрогруппы 1 подаются тактовые импульсы (вход )6) и принимаемый сигнал (вход 17).

Импульсы с выхода дешифратора 1, опознающего сипхрогруппу в информационном сигнале и дешпфрирующего ее, поступают на блок

2, осуществляющий анализ временного положения откликов дешифратора 1. Блок 2 определяет местоположение импульсов с дешифратора, при этом критерием отличия периодически следующих откликов и откликов внутри интервала периодичности служит первый отклик с выхода дешифратора, который принимается за предполагаемую позицию .начала цикла.

Импульс, соответствующий первому отклику, запускает управляемый делитель 9 тактовой частоты до частоты циклов, а также через схему «И» 14 поступает на вход прямого счета реверсивного счетчика 10. Появившийся вслед

-a этим внутри цикла хотя бы один отклик с дешифратора синхрогруппы поступает на выход откликов внугри интервала периодичности блока 2 и далее на переброс триггера 4 блока определения сбоев 3.

Второй периодически следующий отклик с дешифратора синхрогруппы (при его наличии) возвращает через схему «ИЛИ» 7 триггер в исходное состояние и поступает на вход прямого счета реверсивного счетчика 10. Если второй отклик с дешифратора отсутствует, то цикловой:импульс с выхода управляемого делителя 9 через схему «И» 6 поступает на входы обратного счета реверсивного счетчика 10 и переброса триггера 4 через схему «ИЛИ» 7.

B случае, когда после появления импульса, соответствующего первому отклику, внутри цикла нет ни одного импульса с дешифратора синхрогруппы и появился второй периодически следующий отклик, то он проходит на вход прямого счета реверсивного, счетчика.

При отсутствии второго периодически следующего отклика на реверсивном счетчике сохраняется предыдущее записанное число, и вновь ведется просмотр следующего интервала внутри цикла. Если в результате счета реверсивный счетчик досчитал до нулевого состояния, то цикловый импульс с выхода управляемого делителя 9 проходит через схему

«И» 5, открываемую по команде с дешифратора 12 через схему «НЕ» 8 и останавливает управляемый делитель, который вновь запустится первым (очередным) откликом с дешифратора 1.

Таким образом, триггер 4 в случае наличия импульса внутри интервала периодичности,и отсутствия очередного периодически следующего отклика с дешифратора синхрогруппы дает разрешение на прохождение цикловых импульсов на вход обратного счета реверсивного счетчика 10 при любом состоянии последнего, кроме нулевого, а при списывании реверсивного счетчика в ноль — также и на остановку управляемого делителя 9. Если в результате счета реверсивный счегчик досчитал до заданной цифры, триггер индикации 13 состояния синхронизма по команде с дешифратора 11 переключается в положение, соответствующее установившемуся режиму устройстства, а сам реверсивный счетчик переходит в состояние, соответствующее максимально возможной цифре прямого счета. Теперь все периодически следующие отклики поступают через схему «И» 15 на вход установки реверсивного счетчика, переключая последний с любой цифры, кроме нулевой, в состояние,соответствующее максимально возможной цифре прямого счета. Поступление импульсов на вход обратного счета реверсивного счетчика происходит аналогично вышеописанному в переходном режиме.

При списании реверсивного счетчика до нуля триггер индикации 13 по команде с дешифратора 12 переходит в положение, соответствующее переходному режиму устроиства, при этом также происходит остановка управляемого делителя 9, и вновь начинается поиск истинной позиции начала цикла.

Предмет изобретения

1. Устройство для синхронизации по циклам, содержащее последовательно соединенные дешифратор синхрогруппы, блок анализа и управляемый делитель, выход которого подключен к выходу устройства, первый вход устройства соединен с первыми входами управляемого делителя и дешифра1ора синхрогруппы, второй вход которого подключен ко второму входу устройства, схемы «И», блок определения сбоев и реверсивный счетчик с подключенным к нему через дешифраторы нулевого и заданного состояний триггером .индикации, отличающееся тем, что, с целью повышения помехоустойчивости, в устройстве первый выход блока анализа, соединенный с первыми входами двух схем «И», и второй выход блока анализа подключены соответственно к первому и второму входам блока определения сбоев, управляющий вход которого соединен с выходом дешифратора нулевого состояния, третий вход блока определения сбоев соединен с выходом управляемого делителя и входом блока анализа, первый и второй выходы блока определения сбоев подключены соответственно ко второму входу управляемого делителя и ко входу обратного счета реверсивного счетчика, вторые входу схем «И» подключены соответственно к первому и второму выходам триггера индикации, выходы схем

«И» соединены соответственно со входом установки и входом прямого счета реверсивного счетчика.

439936

Составитель А. Жеренов

Техред T. Миронова

Редактор Е. Семанова

Корректор А. Дзесова

Заказ 3718/17 Изд. № 1897 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

2. Устройство по п. 1, отлича ющееся тем, что в нем блок определения сбоев содержит схемы «И», «ИЛИ», «НЕ» .и триггер, подключенный первым входом через схему

«ИЛИ» к первому входу блока, второй вход схемы «ИЛИ» соединен со вторым выходом блока и выходом первой схемы «И», второй вход блока подключен ко второму входу триггера, выход которого подключен к первым входам первой и второй схем «И», вторые входы которых подсоединены к третьему входу блока, управляющий вход которого подключен к третьему входу первой схемы «И» и через схему «HE» — к третьему входу второй схемы «И», выход которой соединен с первым выходом блока.