Устройство подавления флуктуационных помех

Иллюстрации

Показать всеРеферат

т

Союз т;.оветсних (и 4зфф42

Социалистических

Республик

И3ОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) Заявлено 03,03.72 (21) 1754969/26-9 с присоединением заявки №вЂ” (32) Пр нор итств

Оп бликов»но 15.08.74. Бюллетень ¹ 30 (51) М.Кл. Н 04п 5/14

Гасударственный комитет

Совета Министров СССР оа делам изооретений и открытий (53) УДК 621.397.231 (088.8) Дата опубликования описания 02.04.75 (72) Авто ры изобретении

8. И. Кваша, Г. М. Родов и С. М. Шерайзин

Всесоюзный заочный электротехнический институт связи (71) Заявитель (54) УС|РОЙСТВО ПОДАВЛЕНИЯ ФЛУКТУАЦИОННЪ|Х

ПОМЕХ

Изобретение относится к телевизионной технике. Устройство позволяет уменьшить уровень флуктуациоииых помех в видеосигнале черно-белого и цветного телевидения без ухудшения четкости и резкости изображения.

Известно устройство, содержащее смеситель, один вход которого соединен со входом устройства через фильтр нижних частот, а второй вход — через последовательно соединенные фильтр верхних частот и ограничитель по минимуму для уменьшения уровня помех. Однако в данном устройстве снижение уровня помех сопровождается значительными искажениями видеосигнала. Потому реально достижимая степень подавления помех, определяемая допустимыми искажениями видеосигнала, невысока.

С целью повышения степени подавления помех ко второму входу схемы запрета подключены выходы двух схем совпадения и выход второго смесителя, причем один из входов обеих схем совпадения соединен непосредственно, а второй вход — через линию задержки с выходами инверсного каскада, вход которого соединен с выходом упомянутого дифференцирующего усилителя, а входы второго смесителя соединены со входом устройства через линию задержки и инвертор.

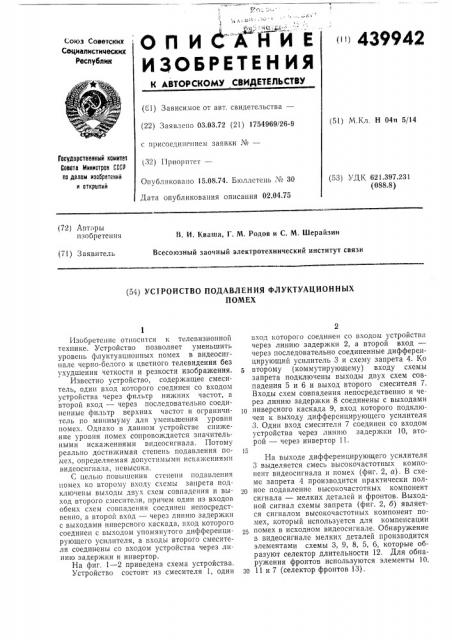

На фиг. 1 — 2 приведена схема устройства.

Устройство состоит из смесителя 1, один вход которого соединен со входом устройств» через линию задержки 2, а второй вход— через последовательно соединенные дифференцирующий усилитель 3 и схему запрета 4. Ко второму (коммутирующему) входу схемы запрета подключены выходы двух схем совпадения 5 и 6 и выход второго смесителя 7.

Входы схем совпадения непосредственно и через линию задержки 8 соединены с выходами

1р инверсного каскада 9, вход которого подключен к выходу дифференцирующего усилителя

3. Один вход смесителя 7 соединен со входом устройства через линию задержки 10, второй — через инвертор !1.

На выходе дифференцирующего усилителя

3 выделяется смесь высокочастотных компонент видеосигнала и помех (фиг. 2, а). В схеме запрета 4 производится практически полное подавление высокочастотных компонент сигнала — мелких деталей и фронтов. Выходной сигнал схемы запрета (фиг. 2, б) является сигналом высокочастотных компонент помех, который используется для компенсации помех в исходном видеосигнале. Обнаружение в видеосигнале мелких деталей производится элементами схемы 3, 9, 8, 5, 6, которые образуют селектор длительности 12. Для обнаружения фронтов используются элементы 10, 30 11 и 7 (селектор фронтов 13).

439942

IIpедме Г изооpeтеп пи

Устройство подавления флуктуационных помех, содержащее первый смеситель, один из входов которого соединен со входом устройства через линию задержки, а второй вход— через последовательно соединенные дифференцирующий усилитель и схему запрета, отличающееся тем, что, с целью повышения степени подавления помех, ко второму входу схемы запрета подключены выходы двух схем совпадения и выход второго смесителя, причем один из входов обеих схем совпадения соединен непосредственно, а второй вход — через линию задержки с выходами инверсного каскада, вход которого соединен с выходом упомянутого дифференцирующего усилителя, а входы второго смесителя соединены со входом устройства через линию задержки и инвертор.

439942

Редактор Л. Цветкова

Коррекгор T. Гревцов;

Заказ 7323 Изд. № 1913 Тираж 678

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5

Подписное

МОТ, Загорский цех

U, Составитель С. Шерайзин

Техред Т. Курилко