Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

б

О П И C А Н--M— -.":Е- и-44О796

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 02.07,72 (21) 1795050/26-9!.51) тч. Кл. H 03k 13/20 с присосдипением заявки М 1795051/26-9

Госудорствеииый комитет

Совете Министров СССР по делом нзебоетений (32) Приоритет I

Опубликовано 25.08.74. Бюллетень № 31

Дата опубликования описания 14.07.75 у ьк qT-ттл r пl, --ют Оц g)

1 открытии (72) Авторы изобретения

Е. И. Михайлов, E. М. Е1еремет и В. Б. Денисюк

Львовский завод электроизмерительных приборов (71) Заявитель (54) АНАЛ;". ГЗ.",! . > - ÎÂÎ 1 11Г! ()Б.: АЗОВА 1 кЕЛЬ

Изобретение относится к аналого-цифровым преобразователям (ЛЦП), применяемых в различных областях измерительной техники, особенно в системах автоматической обработки информации и т. д.

Известен аналого-цифровой преобразователь, содержащий источник опорного напряжения, два электронных ключа, интегратор, компаратор уровня, логическое устройство, регистрирующий счетчик, устройство автоматики, генератор импульсов заполнения, причем вход первого ключа подключен к источнику преобразуемого напряжения, а выход через интегратор, компаратор уровня и логическое устройство — к первому входу регистрирующего счетчика; вход второго ключа соединен с источником опорного напряжения, а выход— с выходом первого ключа; выход генератора импульсов заполнения подключен ко второму входу логического устройства; второй вход регистриру1ощего счетчика соединен с вторым выходом устройства автоматики, второй вход которого соединен с выходом регистрирующего счетчика, а третий его вход и третий вход регистрирующего счетчика подключен к источнику сети 50 гц.

Однако нзвсстному АЦП, работающему по принципу двойного интегрирования при условии подавления сетевой помехи с частотой

50 гц свойственна значительная величина цикла преобразования — более 20 мсек. Это ограничивает возможности систем автоматической обработки информация и т. д.

Цель изобретения — уменьшение времени

5 преобразования АЦП при наличии сетевой помехи и повышение его быстродействия.

Предлагаемое устройство отличается от известных тем, что в него дополнительно вводят10 ся источник опорного напряжени",, второй интегратор, второй компаратор, третий и четвертый ключи; причем вход третьего ключа соединен с дополнительным источником опорного напряжения, а выход через второй интегра15 тор и второй компаратор уровня — с четвертым входом устройства автоматики; вход четгертого ключа соединен с входом второго ключа, а его выход — с выходом третьего. Кроме того, с целью повышения быстродействия в не20 го введены генератор импульсов управляемой длителhlloñòè, схема управления, пятый и шестой ключи, причем второй выход генератора импульсов заполнения соединен через пятый ключ с четвертым входом регистрирующего

25 счетчика, второй выход которого через шестой ключ и схему управления соединен с генератором импульсов управляемой длительности, выход которого соедпнеkl со вторым входом схемы управ."ения и пятым ьходом устройства

30 автоматики.

44079О

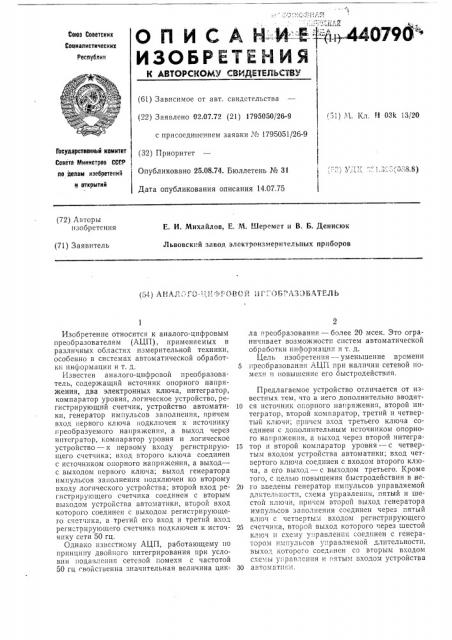

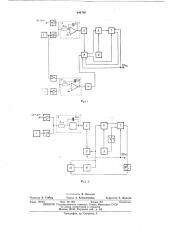

На фпг. 1 представлена структурная схема описываемого устройства, первый вариант; на фиг. 2 — то же, второй вариант.

Аналого-цифровой преобразователь состоит пз источника 1 опорного напряжения Uo(, 5 электронных ключей 2 и 3, интегратора 4, компаратора уровня 5, логического устройства б, регистрирующего счетчика 7 емкостью и( единиц, устройства автоматики 8, генератора импульсов 9 заполнения частотой f(, источни- 10 ка 10 опорного напряжения — Uo, электронных ключей 11 и 12, интегратора 13, компаратора уровня 14, генератора импульсов 15 управляемой длительности, схемы 1б управления, электронных ключей 17 и 18, преобразу- 15 емого напряжения Uia и напряжения сетевой помехи U

U = — UÄ sin((ot+ з).

Синхронизация работы всего устройства 20 производится от сети 50 гц при помощи устройства азтоматикп, которое вырабатывает командные импульсы при прохождении синхронизпруюп.его напряжения через нулевой уровень, т. с. с периодом 10 мсек. 25

В исходном состоянии напряжение на выходе интегратора 4 равно нулю; конденсатор

С„о ((нтегратора 13 предварительно заряжен до величины

U, = — " -, где Т, =- — и„

R,a С,г Л все ключи разомкнуты.

С первым переходом синхронизирующего напряжения 50 гц через нулевой уровень по 35 команде от устройства автоматики замыкак)тся ключи 2 и 11; начинается первый такт интегрирования преобразуемого напряжения.

Первый такт оканчивается, когда напряжение на выходе интегратора 13 станет равно 40 нулю. По команде от компаратора 14 устройства автоматики 8 ключи 2 и 11 размыкаются.

Длительность такта равна

-р Ut Ria Cia Uoa Т1-R a C,г г— 45

Uo1 Uo1 при JU„J —.. )U„), Т,=Т,, Напряжсние на выходе интегратора 4 достигнет величины 50 ю и, — ) (и.+иД о (»i+;)(e. (ц

Ra, С„,, о

Второй такт интегрирования преобразуемого напряжения начинается при очередном переходе синхронизирующего напряжения через нулевой уровень, т. е. через 10 мсек, когда начальный сдвиг фазы напр)(жения помехи б,.- 60 лет иметь величину о(+ср. В этот момент по команде от устройства автоматики замыкаются ключи 2 и 12; производится сброс в исходное состояние счетчика 12 и начинается его заполнение импульсами от генератора 9. 65

Второй такт заканчивается в момент переполнения индикаторного счетчика, когда на его вход поступит а(импульсов, а на его выходе появится импульс переполнения. Длительность второго такта равна

1 — n.„= Т,, Л

Напряжение на выходе интегратора 13 достигнет величины

U Uo1 Т1

1 1

Ra, С,, а на выходе интегратора 4 величины т, и, =U,+ ) (U„+U, sin((+-,. + w)(dt о пли с учетом (1)

U,=- 2 (2)

R„„Ca1

После переполнения регистрирующего счетчика начинается разряд интегратора 4 от источника опорного напряжения 1. При этом ключ 3 замыкается, а остальные размыкаются. Когда напряжение на выходе интегратора

4 становится равно нулю, по команде от компаратора 5 устройства автоматики ключ 3 размыкается, заполнение счетчика прекращается, схема возвращается в исходное состояние.

Время разряда Тз интегратора 4 равно у Ua Ru 1 Cii1 з— > О1 с учетом (2)

Т,=U

1 о(Количество импульсов A (, поступивших на вход регистрирующего счетчика 7, за время

Тз равно у я Т f1.Uõ 2Т1 их.2 f, п1

1 — 11 г— о1 о1 Л

У01

2п, где и = — — коэффициент преобразования. О1

В случае, если Т +Тз менее 10 мсек, предлагаемое устройство позволяет производить преобразование аналог — код при подавлении сетевой помехи за время менее 20 мсек, Синхронизация работы устройства, представленного на фиг. 2, производится, как и в первом варианте, от сети 50 гц.

Б исходном состоянии напряжение на выходе интегратора 4 равно нулю. Все ключи разомкнуты. Первый такт интегрирования преобразуемого напряжения начинается в момент прохождения сетевого синхронизирующего напряжения через нулевой уровень, В этот момент запускается генератор 15 и замыкается

440790

U„2 Т

1 и I и1 (3) ключ 2. Длительность первого такта определяется длительностью выходного импульса генератора 15, после окончания которого ключ 2 размыкается.

Второй такт интегрирования преобразуемого напряжения начинается в очередной момент прохождения сетевого синхронизирующего напряжения через нулевой уровень, Таким образом, начальный сдвиг фазы напряжения помехи во второй такт будет равен ср+л.

В момент начала второго такта интегрирования в схеме по команде от автоматики замыкаются ключи 2, 17, 18, производится сброс показаний регистрирующего счетчика и начинается его заполнение от генератора 9.

Длительность второго такта интегрирования преобразуемого напряжения также определяется длительностью выходного импульса генератора 15. Одновременно, во время второго такта интегрирования при помощи схемы управления 16 производится подстройка длительности выходного импульса генератора 15 таким образом, чтобы она стала равна времени заполнения счетчика 7. В течение нескольких циклов преобразования (с момента включения) длительность импульса Т4 на выходе генератора становится равна

Т,.=- и,. —.

Поэтому второй такт интегрирования заканчивается в момент заполнения счетчика 7, когда он возвращается в исходное состояние.

В этот момент по команде от автоматики ключи 2, 17, 18 размыкаются; ключ 3 замыкается, счетчик продолжает заполняться через логическое устройство 6. Начинается разряд интегратора 4 от источника 1 опорного напряжения.

Напряжение U; на выходе интегратора 4 к моменту разряда будет иметь величину т, U, = (У +U„sin(t+ р))dt+ о т, + i (U„+U„sin(mt+-,.+q))dt )= о

Когда напряжение на выходе интегратора 4 становится равным нулю, по команде от компаратора 5 и автоматики ключ 3 размыкается и заполнение счетчика прекращается; схема возвращается в исходное состояние.

Время разряда Т5 интегратора 4 равно

Т, == " " ; с учетом (3)

00 R1 С01 01

Т, = U„. 01

Количество импульсов N2, поступивших на вход регистрирующего счетчика 7 за время Т5, равно

У 0 У Л 11х 2Т4 Л 2t -t» 11)

0 !1 0 01 01 Л

01

2п, где 1 = — — коэффициент преобразования 101

В случае, если Т4+Т, менее 10 мсек, предлагаемое устройство позволяет производить преобразование аналог — код при подавлении сетевой помехи за время менее 20 мсек.

В случае визуальной индикации результатов преобразования для обеспечения «немигающего» отсчета напряжение «поджига» индикаторных ламп производится в первый такт интегрирования преобразуемого напряжения.

Предмет изобретения

1. Аналого-цифровой преобразователь, содержащий источник опорного напряжения, два электронных ключа, интегратор, компаратор уровня, логическое устройство, регистрирующий счетчик, устройство автоматики, генератор импульсов заполнения, причем вход первого ключа подключен к источнику преобразуемого напряжения, а выход через интегратор, компаратор уровня и логическое устройство— к первому входу регистрирующего счетчика, вход второго ключа соединен с источником опорного напряжения, а выход — с выходом первого ключа, выход генератора импульсов заполнения подключен ко второму входу логического устройства, второй вход регистрирующего счетчика соединен со вторым выходом устройства автоматики, второй вход которого соединен с выходом регистрирующего счетчика, а третий его вход и третий вход регистрирующего счетчика подключены к источнику сети 50 гц, отличающийся тем, что, с целью уменьшения времени преобразования при наличии сетевой помехи, в схему введены дополнительно источник опорного напряжения, второй интегратор, второй компаратор и третий и четвертый ключи, причем вход третьего ключа соединен с дополнительным источником опорного напряжения, а выход через второй интегратор и второй компаратор уровня — с четвертым входом устройства автоматики, вход четвертого ключа соединен со входом второго ключа, а его выход — с выходом третьего. 2. Преобразователь по п. 1, о тл и ч а юшийся тем, что, с целью повышения быстродействия, в него введены генератор импульсов, управляемой длительности схема управления, пятый и шестой ключи, причем второй выход генератора импульсов заполнения соединен через пятый ключ с четвертым входом регистрирующего счетчика, второй выход которого через шестой ключ и схему управления соединен с генератором импульсов управляемой длительности, выход которого соединен со вторым входом схемы управления и пятым входом устройства автоматики.

440790

v -u 7иг !

@иГ 2

Редактор Е. Гончар

Корректор А. Дзесова

Заказ 1974/3 Изд. № 203 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж 35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ./к + V

Я Я

Составитель В. Денисюк

Техред А. Камышникова