Устройство для автоматического выбора каналов

Иллюстрации

Показать всеРеферат

О П И C-А-"-Н.:И..

ИЗОБРЕТЕНИЯ (и) 440798

Союз Советскими

Социалистим вских

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 14.03.72 (21) 1758640/26-9 (51) М. Кл. Н 04b 1/10 с присоединением заявки №

Государственный комитет

Совета Министров СССР по делам изсоретений и открытий (32) Приоритет

Опубликовано 25,08.74. Бюллетень № 31

Дата опубликования описания 03.02.75 (53) УДК 621.396.668.8 (088.8) (72) Авторы изобретения В. А. Писарев, В. И. Криушонков, А. А. Гришуков и В. К. Решемкин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ВЫБОРА

КАНАЛОВ

Изобретение относится к радиотехнике, в частности к техникс приема сигналов в системах связи с разнесенным приемом при асинхронных методах демодуляции.

Известное устройство для автоматического выбора канала или ветви разнесения с наименьшими искажениями сигнала в условиях действия различных аддитивных и мультипликативных.

В известном устройстве для автоматического выбора канала или ветви разнесения с наименьшими искажениями сигнала в условиях действия различных аддитивных и мультипликативных помех, в котором используются асинхронные методы модуляции, реализуется энергетический критерий, когда решение о выборе канала выносится путем сравнения энергии смеси сигнала и помехи, присутствующих в каждом канале.

Известное устройство содержит общий линейный тракт, .подсоединенный параллельно к входам трех каналов разнесения, каждый из которых содержит канальный фильтр и асинхронный демодулятор, подключенный через канальный ключ к сумматору, выход которого является выходом устройства для автоматического выбора каналов, каждый же асинхронный демодулятор подключен через блок преобразования к блоку сравнения, выходы которого, соответствующие данному каналу, через блок решения подключены к канальным ключам.

Однако известное устройство имеет недостаточную надежность и помехозащищенность.

Целью изобретения является повышение надежности и помехозащищенностп устройства.

Для этого блок преобразования содержит

10 три одинаковых тракта, подсоединенных по входам и выходам к соответствующим канальным входам и выходам блока преобразования, в каждом тракте блока преобразования последовательно включены двусторонний огра15 ничитель, первая дифференцирующая цепочка и своим первым входом и выходом первая схема «ИЛИ», к второму входу которой через схему «НЕ» и вторую дифференцирующую цепочку подсоединен выход двустороннего огра20 ничителя, блок сравнения содержит тр верспвных счетчика, причем соотве- 1ий первый канальный вход блока сключен к первому входу реве. ка первого канала и к вт

25 сивного счетчика трет ф вующий второй кап „ф ния подключен к счетчика втор реверсивно" p+ ...с »

30 ветствур„3

440798 сравнения подключен к первому входу реверсивного счетчика третьего канала и к второму входу реверсивного счетчика второго канала, решающий блок содержит первый триггер, первый и второй входы которого подсоединены соответственно к паре входов решающего блока, соответствующей первому каналу, а первый выход первого триггера подключен параллельно к первым входам первой и второй схем «И», ко вторым входам которых подсоединены соответственно первый и второй выходы третьего триггера, подключенного по первому и второму входам к паре входов решающего блока, соответствующей третьему каналу, выход первой схемы «И» подсоединен к второму входу третьего канального ключа, вторая схема «И» своим выходом подключена через первый вход и выход схемы «ИЛИ» решающего блока к второму входу второго канального ключа, второй выход первого триггера подключен параллельно к первым входам третьей и четвертой схем «И», к вторым входам которых через первые входы и выходы и вторые входы и выходы второго триггера соответственно подсоединена пара входов решающего блока, соответствующая второму каналу, выход третьей схемы «И» подключен к второму входу первого канального ключа, а выход четвертой схемы «И» подсоединен к второму входу схемы «ИЛИ» решающего блока.

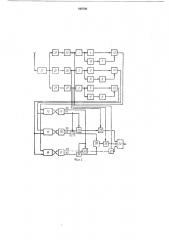

Изобретение пояснено чертежами.

На фиг. 1 приведена блок-схема устройства; на фиг, 2 — эпюры сигналов на выходах соответствующих элементов блок-схемы.

Устройство для автоматического выбора каналов содержит три блока — блок преобразования, блок сравнения и решающий блок.

Блок преобразования содержит три одинаковых тракта, каждый из которых состоит соответственно из двусторонних ограничителей

1, 2, 3, первых дифференцирующих цепочек 4, 5, 6, вторых дифференцирующих цепочек 7, 8, 9, схем «НЕ» 10, 11, 12, первых схем «ИЛИ»

13, 14, 15.

Блок сравнения содержит три реверсивных счетчика 16, 17, 18.

Решающий блок содержит триггеры 19, 20, 21, схемы «И» 22, 23, 24, 25 и вторую схему

«ИЛИ» 26. Кроме этого в устройство входят канальные ключи 27, 28, 29, сумматор 30, радиоприемник 31, канальные фильтры 32, 33, 34 и асинхронные демодуляторы 35, 36, 37.

При таком выполнении устройства автоматический выбор канала или ветви разнесения происходит по наибольшему отношению спгн ал/пом ех а.

Устройство работает следующим образом.

Сигнал от приемника 31 через канальные фильтры 32, 33, 34, которые разделяют спектры частотно-разнесенных сигналов (AT, ЧТ, ФРИ, и т. д.) поступает на входы асинхронемодуляторов 35, 36, 37, к выходам ко"очены схемы блока преобразова- ений в непрерывную одно1О

65 полярную последовательность коротких импульсов.

Сигналы с демодуляторов (см. фиг. 2, а, 6, в) поступают на двусторонние ограничители

1, 2, 3, ограничиваются ими и подаются на первые дифференцирующие цепочки 4, 5, б и схемы «НЕ» (инвенторов) 10, 11, 12, после инвентирования они поступают на вторые дифференцирующие цепочки 7, 8, 9.

Выходы дифференцирующих цепочек схемы преобразования каждого канала соответственно объединены схемами «ИЛИ» 13, 14, 15. Две цепочки дифференцирования необходимы для того, чтобы определить нулевые пересечения искаженного помехой сигнала как в положительном, так и в отрицательном направлениях, так как это увеличивает в два раза число пересечений за единицу времени, что позволяет повысить разрешающую способность всего прибора и уменьшить его инерционность.

Положительные импульсы, соответствующие нулевым пересечениям сигналов на выходе демодуляторов, с выходов блока преобразователя поступают на соответствующие входы счетчиков 16, 17, 18. Введение реверсивных счетчиков 16, 17, 18 в блок сравнения позволяет вычислять текущую разность числа импульсов с двух каналов (усреднение на скользящем интервале времени). Как только разность числа импульсов превзойдет емкость реверсивного с етчика, сразу же автоматически сформируется сигнал, определяющий какой из сравниваемых каналов лучше по качеству передаваемой информации.

Лучшим из двух каналов будет тот, для которого алгебраическая разность числа нулевых пересечений отрицательна. При этом не требуется специального датчика интервала времени, а начало счета и сброс показаний в реверсивном счетчике происходят BBTOMBTHчески. В момент превышения установленной емкости счетчика блок сравнения формирует единичный короткий импульс, поступающий на вход решающего блока.

Состояние триггеров с раздельным запуском 19, 20, 21 отражает результат сравнения каналов. Канальные ключи 27, 28, 29, на которые подаются сигналы с выходов демодуляторов, коммутируются выходными сигналами, соответственно поступающими со схем «И» 25, «ИЛИ» 26, «И» 23, Ре пающий блок работает следующим образом.

Если первый канал лучше второго, то канальный ключ 28 переводится в закрытое состояние; при этом окончательное решение выносится при сравнении первого и третьего каналов, если первый канал хуже второго, то ключ 27 переводится в закрытое состояние; при этом окончательное решение выносится при сравнении только второго и третьего каналов.

Пусть начальное состояние управляющих триггеров 19, 20, 21 «единица» по выходам 38, 39, 40 и «нуль» по выходам 41, 42, 43 (см, 440798

5 фиг, 2, з, к, м), где состоянию «нуль» соответствует более высокий потенциал. Все схемы

«И» 22, 23, 24, 25 открываются при подаче на оба входа напряжения, соответствующего состоянию «нуль». Тогда ключ 28 замыкается выходным напряжением схемы «И» 22 через схему «ИЛИ» 26, а ключи 27 и 29 остаются разомкнутыми, Если первый канал станет лучше второго, а второй — лучше третьего, тогда в момент времени t, переполненный счетчик 18 опрокидывает триггер 21 (см. фиг. 2, л, м, и). Триггер 21 переходит в состояние «нуль» по выходу 39 и на вход схемы «И» 25 подается положительное напряжение. Схема «И» 25 закрыта по другому входу. Схема «И» 24 дополнительно закрывается по входу 39. Состояние всех остальных схем остается без изменений.

В момент времени t> после переполнения счетчика 16 опрокидывается триггер 19 (см. фиг. 2, лс, з), переходя по выходу 38 в состояние «нуль». Этим закрывается схема «И» 22, размыкая через схему «ИЛИ» 26 канальный ключ 28. В это же время полностью открывается схема «И» 25 и замыкает канальный ключ 27.

Таким образом, в момент времени 1 на вход сумматора 30 вместо третьего канала приемника подключается первый канал. В моменты времени t>, t„подтверждается включение первого канала и перекоммутации каналов не происходит.

Если второй канал станет лучше первого, но хуже третьего, в этом случае схемы «И»

24, 25 закрываются выходом 38, размыкая канальный ключ 27, а схемы «И» 22, 23 открываются выходом 38. В это же время схема

«И» 23 закрывается выходом 39, а схема «И»

22 открывается выходом 39, тем самым через схему «ИЛИ» 26 замыкается ключ 28.

Предмет изобр етения

Устройство для автоматического выбора каналов для систем связи с разнесенным приемом при асинхронных методах демодуляции, содержащее общий линейный тракт, подсоединенный параллельно к входам трех каналов разнесения, каждый из которыx содержит последовательно соединенные канальный фильтр и асинхронный демодулятор, подключенный своим выходом через первый вход и выход канального ключа к соответствующему входу сумматора, выход которого является выходом устройства для автоматического выбора каналов, причем каждый асинхронный демодулятор подключен через соответствующий вход и соответствующий выход блока преобразования к соответствующему канальному входу блока сравнения, каждая пара

55 выходов которого, соответствующая данному каналу, в свою очередь через каждую пару входов и выход блока решения, соответствующие данному каналу, подключена ко второму входу канального ключа, о т л и ч а ю щ с сся тем, что, с целью повышения надежности и помехозащищенности, блок преобразования содержит три одинаковых тракта, подсоединенных по входам и выходам к соответствующим канальным входам и выходам блока преобразования, в каждом тракте блока преобразования последовательно включены двусторонний ограничитель, первая дифференцирующая цепочка и своим первым входом и выхо.дом первая схема «ИЛИ», к второму входу которой через схему «НЕ» и вторую дифференцирующую цепочку подсоединен выход двустороннего ограничителя, блок сравнения .содержит три реверсивных счетчика, причем соответствующии первый канальный вход блока сравнения подключен к первому входу реверсивного счетчика первого канала и к второму входу реверсивного счетчика третьего канала, соответствующий второй канальный вхоч блока сравнения подключен к первому входу реверсивного счетчика второго канала и к второму входу реверсивного счетчика первого канала, а соответствующий третий канальный вход блока сравнения подкл,очен к первому входу реверсивного счетчика третьего канала и к второму вход реверсивного счетчика второго канала, решающий блок содержит первый триггер, первый и второй входы которого подсоединены соответственно к паре входов решающего блока. соответствующей первому каналу, а первый выход первого триггера подключен параллельно к первым входам первой и второй схем «И», ко вторым входам которых подсоединены соответственно первый и второй выходы третьего триггера, подключенного по первому и второму входам к паре входов решающего блока, соответствующей третьему каналу, выход первой схемы «И» подсоедпнен к второму входу третьего канального ключа, вторая схема «И» своим выходом подключена через первый вход и выход схемы «ИЛИ» решающего блока к второму входу второго канального ключа, второй выход первого тпиггера подключен параллельно к первым входам третьей и четвертой схем «И», к вторым входам которых через первые входы и выходы и вторые входы и выходы второго триггера соответственно подсоединена пара входов решающего блока. соответствующая второму каналу, выход третьей схемы «И» подключен к второму входу первого канального ключа, а выход четвертой схемы «И» подсоединен к второму входу схемы «ИЛИ» рец ающего блока.

440798

- г иг. 2

Составитель В, Кочнев

Редактор А. Зиньковский Техред Г. Васильева Корректор А, Дзесова

Заказ 162/5 Изд. № 190 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д, 4/5

Типография, пр. Сапунова, 2