Твердотельная матрица для запоминающегося устройства

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii) 44l59I

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 24.08.72 (21) 1823140!18-24 с присоединением заявки № (32) Приоритет

Опубликовано 30.08.74. Бюллетень № 32

Дата опубликования описания 29.07.75 (51) М. Кл. G 1lс 11/40

Гасударственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК 681.327.066 (088.8) (72) Авторы изобретения А. И. Мальцев, В. В. Поспелов, Н. Ф. Трутнев и В. П. Чунихин (71) Заявитель (54) ТВЕРДОТЕЛЬНАЯ МАТРИЦА

ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОИСТВА

Изобретение может быть использовано в вычислительной технике и устройствах автоматики.

Известна матрица для запоминающего устройства, содержащая МДП-транзисторы с изменяемым порогом включения, которые по строкам затворами подключены к управляющим шинам, а по столбцам объединены между собой двумя или более шинами. Последнее обстоятельство приводит к усложнению конст рукции матрицы и требует для ее управления источников положительных и отрицательных сигналов.

Цель изобретения — упрощение конструкции матрицы.

Это достигается тем, что в каждом столбце сток предыдущего транзистора соединен с истоком последующего, при этом исток первого транзистора каждого столбца подключен к шине питания, а сток последнего — к шине считывания.

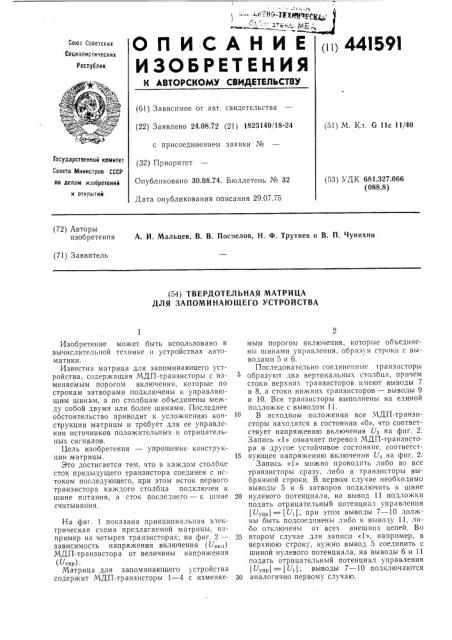

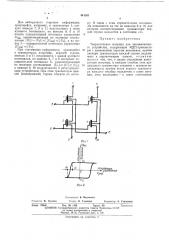

На фиг. 1 показана принципиальная электрическая схема предлагаемой матрицы, например на четырех транзисторах; на фиг, 2— зависимость напряжения включения (Usa )

МДП-транзистора от величины напряжения (ихпр).

Матрица для запоминающего устройства содержит МДП-транзисторы 1 — 4 с изменяемым порогом включения, которые объединены шинами управления, образуя строки с выводами 5 и 6.

Последовательно соединенныс транзисторы образуют два вертикальных столбца, причем стоки верхних транзисторов имеют выводы 7 и 8, а стоки нижних транзисторов — выводы 9 и 10. Все транзисторы выполнены на единой подложке с выводом 11.

10 В исходном положении все МДП-транзисторы находятся в состоянии «О», что соответствует напряжению включения U, на фиг. 2.

Запись «1» означает перевод МДП-транзистора в другое устойчивое состояние, соответст15 вующее напряжению включения U4 на фиг. 2.

Запись «1» можно проводить либо во все транзисторы сразу, либо в транзисторы выбранной строки. В первом случае необходимо выводы 5 и 6 затворов подключить к шине

20 нулевого потенциала, на вывод 11 подложки подать отрицательный потенциал управления ((.тх,р(= U> (, при этом выводы 7 — 10 должны быть подсоединены либо к выводу 11, либо отключены от всех внешних цепей, Во

25 втором случае для записи «1», например, в верхнюю строку, нужно вывод 5 соединить с шиной нулевого потенциала, на выводы 6 и 11 подать отрицательный потенциал управления

J U,-,ð = U<); выводы 7 — 10 подключаются

ЗО аналогично первому случаю. е Ф

441 5 91

Предмет изобретения

Жиг.1

U бкл

5 э ф

04 ф

Ф ь

=С psweeue

° pnpadnpaug

ЦЪг. 2

Составитель В. Надточиев

Редактор И. Грузова Тсхред О. Гуменюк Корректор А. Степанова

Заказ 1708/6 Изд. № 1426 Тираж 591 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, %-35, Раушская наб., д. 4i5

Типография, пр. Сапунова, 2

Для выборочного стирания информации, хранящейся, например, в транзисторе 1, следует выводы 7, 9 и 11 подсоединить к шине нулевого потенциала, на выводы 8, б и 10 подать отрицательный потенциал управления

У,,р, удовлетворяющий по величине соотношению 1 l Uq I — I U211 (1 Уупр1 (1 021, а на вы вод 5 — отрицательный потенциал управления ! 7 1=%1

При считывании информации, хранящейся в транзисторах, например, верхней строки, выводы 5 и 11 соединяются с шиной нулевого потенциала, на выводы б, 7 и 8 посту пает отрицательный потенциал U, удовлетворяющий по величине соотношению I U31(1UI (I V I а выводы 9, 10 подключаются к регистрирующим устройствам. При этом транзисторы нижней (невыбранной) строки отперты по затвору. В связи с этим отрицательные потенциалы появляются на тех из выводов 9 и 10, для которых соответствующие транзисторы первой строки находятся в состоянии «1вь

Твердотельная матрица для запоминающего устройства, содержащая МДП-транзисто10 ры с изменяемым порогом включения, причем затворы транзисторов каждой строки подключены к управляющим шинам, о т л и ч а юща я ся тем, что, с целью упрощения конструкции матрицы, в каждом столбце сток пре15 дыдущего транзистора соединен с истоком последующего, причем исток первого транзистора каждого столбца подключен к шине питания, сток последнего — к шине считывания.