Автоматический синхронизатор с постоянным углом опережения

Иллюстрации

Показать всеРеферат

(11 ) 441628.

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистицеских

Республик

К АВТОРСКОМУ СЬИДЙТВЛЬСТВУ

{61) Зависимое от авт. свидетельстваЗХ9993 (22) Заявлено 03,04.72 (2!) 1767335/

/24-7 с присоединением заявки{51) М Кл.

Н 02 j, 3/43

Гееуднрстеенний кеинтет

Саветн Мннвтрев СССР не денни неоеретеннй н еткрытнй (32) Приоритет—

Опубликоваиа30.08. 74Бюллетень № Э (53) УИК

621. 316.729 (088.8), .Дата опубликования описания>5,>2;7g

В.В.Кушнерев (72) Автор изобретения (7l) Заявитель

{54)АВТОМАТИЧЕСКИЙ СИНХРОНИЗАТОР С ПОСТОЯННЫМ

У1ИОМ ОПЕРЕЖЕНИЯ

По основному авт.св. 3I9993 известен автоматическйй синхронизатор с постоянным углом опережения для генераторов переменного тока например авиационных, сопержапрй выпрямитель, включенйый на напряжение биений, схему сравнения, источник опорного напряжения, логическую схему, выдающую сигйал в случае, если длительность импуль- 1о сов на ее входе больше заданного времени, интегратор и компаратор, включенйые послеповательно, причем один вхоп компаратора йопключен к выходу выпрямителя, другой - д на источник опорного напряжения, е выход интегратора включен на вход схемы сравнения, на другой вход которой подключен второй источник опорного напряжения, а ее выхоп о подключен к логической схеме.

Цель изобретения - повышение надежности работы синхронизатора в системах, в которых возможная частота скольжения может цревышать частоту срабатывания синхрониза тора.

Для этого предлагаемый синхронизатор снабжен вторым выпрямителем, подключаемым к разноименным фазам генератора и сети, включенными последовательно с йим вторым компаратором, вторым интегратором и второй схемой сравнения, а также пи@фереяциатором,инвертором и выходным триггером со схемами совпадения на входах, Выход первой схемы сравнения подключен непосредственно к первому вхопу схемы совпадения, включенной на записывающий "едийицу" вход триггера, через инвертор - к первому входу схемы совпадения, включенной на записывающий "нульи вход триггера; а выход второ схемы сравнения йодключен ко вторым входам схемы совпадения через дифференциатор.

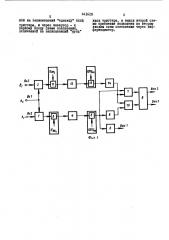

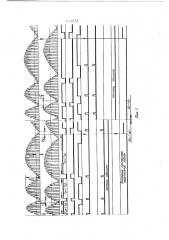

На уиг. I приведена блок-схема преплагаемого синхронизатора; на фиг.2 - диаграммы сигналов в различйых точках атой схемы.

Напряжения с фаз генератора и сети подаются на входы выпрямителей 1 и 2, причем на выпрямитель

1 попаются напряжения с опноименных фаз, а на выпрямитель 2 — с разноименных фаз генератора и сети. Таким образом, на нхопы схемы пойаются сдедуюцие напряжения:

Вх. I — напряжение с фазы А сети 4< - /,ч жЦ ф

Вх. 2 — напряжение с фазы А генератора 4r =Ц, амит, Вх. 3 — напряжение с фазы В генератора 8 =U Дьи(о,ф +Ci), гпе P — амплитуда Йапряжений;

,(Д, — частоты сети и генератора.

Вйхоп выпрямителя I через компаратор 3, интегратор 4 и схему сравнения 5 йодключен непосредственно к вхопу логической схемы 6 и к первому нхопу схемы совпапения 7, включенной на записывающий "епиницу" нхоп триггера 8, и через иннертор 9, попсоепиненной к первому входу схемы совпапения IO, вкдюченной на записывающий "нуль" вход триггера 8.

Выход выпрямителя 2 через компаратор II интегратор Ia, схему сравнения 13 и пифференциатор

I4 попключен ко вторым входам схем сонпапения 7 и IO.

Как видно из фиг. I, напряжение на выходе блока I имеет вип:

И,--/Л -A /= 0 S . . о 4, Напряжение на восходе блока 2:

Ъ=)А . В (=и!у(4Я ) Мф

Or»oàêö»å напряжений на выходах + блоков I и 2:

L, = è.(ì(Ю/ ; =lv /малю - 3> гпе А и ы=- у- частота скольжения.

Как видно из фиг. 2, на выхопе блока 5 имеются прямоугольные импульсы длительностью, ранной времени превышения напряжения Ц нап опорным напряжениемЯ„=,Ц МЯм®и, гпе „, — требуемый угол опережения.

На выходе блока ХЗ имеются прямоугольные импульсы плительностью, равной времени превышения напряжения Я нап опорным наU.ï - g.Ц и =()щ

Как нипно из девой гасти .пиаграмм, при частоте генератора ниже частоты сети, т.е. при йШ . д, сигнал на зайисйвающем "епиницу" входе триггера 8(или на выходе блока 7) отсутствует, так как выходные сигналы от блоков 5 и I4 нв совпадают по времени. В то же время на записывающем "йуль" вхопв

Автоматический синхронизатор с постоянным углом опережения ао авт. св. 319993, о т л и ч а ю щ и й— с я тем, что, с целью повышения напежности работы, он снабжен вторым пнухполупериойным выпрямителем, подключенным на разноименные фазй генератора и сети, последовательно включенными с ним вторым компаратором, вторым интегратором и выхопным триггером со cxeMoN сравнении,а также дифферейциаторои инверторой и входными триггерои оо схемами совпадения на входах, при зтои выход первой схемы сравнения подключен непосредственно к первому входу схеиы совпадения,включенф триггера 8 (т.е. на выхопе блока

IU) имеется серия импульсов, так как всякий раз появление сигнала на выхо.пе блока I4 происхо.пит в тот момент, когда на выхопе блока

Э уже имеется сигнал. Таким образом, при частоте генератора ниже частоты сети триггер И находится в первом, устойчивом состоянии с сигналом на третьем выходе "частоту повысить".

При частоте генератора выше частоты сети, т.е. при Л и) -0, напряжение О имеет такой же вид как и при йи3 рср, а напряжение у принимает вид: щ-ря(, (пап. Д,, т. е. фазоныи сдвиг между напряженйямй p и t) изменяет свой знаку.

Как йипно из правой части .пиаграмм в этом случае на ныхопе блока 7 появляются импульсы, так как появление сигнала на выхопе бдока I4 происходит в тот момент, когда на выхопе блока 5 уже имеется сигнал. На выхопе блока IO импульсы отсутствуют, так как выходные сигналы блоков 9 и I4 не совпа дают по времени. Таким образом, при частоте генератора выше частоты сети триггер 8 устанавливается во второе устоичивое состояние с сигнапон на второы выходе "частоту с+ понизить".

Из фиг.2 видно, что сигнал на перном выхойе появляется в том с лучае, ес ди длите льность импу льсон на выходе блока 5 больше заданной, т.е. частота скольжения меньше частоты срабатывания синхронизатора.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

44l628 б ной на записывающий единицу" вход вход триггера, а выхои втоРой схетриггера, и через инвертор - к мы сравнения йо.цключен ко вторым первому входу схемы совпацения, входам схем совпадения через,цифВклвченной на записывавший "нуь" ференциатор.

Ас