Многодекадное пересчетное устройство с управляемым коэффициентом пересчета

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (») 441672

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 13.10.72 (21) 1838639/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 30.08.74. Бюллетень № 32

Дата опубликования описания 28.04.75 (51) М, Кл. H 03k 23/24

Государственный комитет

Совета Министров СССР (53) УДК 621.374.4 (088.8) ло делам изобретений ,1 и открытий (72) Авторы изобретения

Ю. Н. Артюх, Г. И. Готлиб и В. Я. Загурский (71) Заявитель

Институт электроники и вычислительной техники

АН Латвийской ССР (54) МНОГОДЕКАДНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО

С УПРАВЛЯЕМЫМ КОЭФФИЦИЕНТОМ ПЕРЕСЧЕТА

Изобретение относится к области автоматики и телемеханики, в частности к пересчетным устройствам с управляемым коэффициентом пересчета на основе двоичных счетчиков.

Известны пересчетные устройства с управляемым коэффициентом, содержащие многокаскадные счетчики, схемы совпадения и схемы перезаписи кода.

Работа известных устройств основана на выделении схемой совпадения момента заполнения счетчика, после чего в счетчик через схемы перезаписи заносится код, обратный коэффициенту пересчета.

Однако при нечетных коэффициентах пересчета счетчик работает с удвоенной частотой по отношению к частоте входного сигнала.

Это ограничивает верхнюю частоту счета устройства в целом.

С целью повышения быстродействия устройства в нем выход схемы совпадения и вход устройства подключены соответственно к первому и второму входам дополнительного вентиля, выход которого соединен с схемой записи кода, а триггер младшего разряда первой декады снабжен входом запрета установления в нем единичного состояния, который соединен с выходом схемы записи кода в этот разРяд.

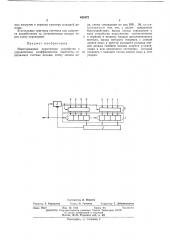

На чертеже показана схема предлагаемого ,стройства.

Устройство содержит многодекадный счетчик 1, каждая из декад которого работает в коде 1 — 2 4 8, схему совпадения 2, подключенную к выходам старшего и младшего разряда всех декад, кроме младшего разряда первой декады. Выход схемы совпадения 2 управляет вентилем 3, выход которого связан с схемой 4 занесения кода.

1р Предположим, что в исходном состоянии в счетчик записан код, обратный коду коэффициента пересчета. В процессе счета происходит последовательное заполнение счетных декад. Сигнал на выходе схемы совпадения 2

15 появляется в такт, предшествующий такту перезаписи кода (код счетчика 999... 98) и разрешает прохождение входного сигнала через вентиль 3. В такт перезаписи при воздействии входного сигнала на выходе вентиля образуется сигнал перезаписи кода. Воздействие сигнала перезаписи на первый триггер заключается в том, что он блокирует изменение его нулевого состояния для нечетных коэффициентов либо разрешает переключение в «единицу» под воздействием входного импульса. В соответствии с указанным принципом работы устройства частота переключений первого триггера младшей декады не превышает входной частоты; для выделения момента перезаписи не требуется подключение дополнитель441672

Предмет изобретения

Составитель Л. Перлова

Редактор Е. Караулова Техред О. Гуменюк Корректор Т. Добровольская

Заказ 964/7 Изд. Ив 1193 Тираж 811 Подписпо"

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ных нагрузок к первому триггеру младшей декады.

В остальные триггеры счетчика код заносится воздействием по установочным входам через схему перезаписи.

Многодекадное пер есчетное устройство с управляемым коэффициентом пересчета, содержащее счетные декады, схему записи кода, схему совпадения на код 999 ... 98, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, выход схемы совпадения и вход устройства подключены соответственно

5 к первому и второму входам дополнительного вентиля, выход которого соединен с схемой записи кода, а триггер младшего разряда первой декады снабжен входом запрета установления в нем единичного состояния, который

10 соединен с выходом схемы записи кода в этот разряд.