Частотный манипулятор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (11) 441679

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) ЗаявленоП ХО ° 72 (21К8379ТЗ/26-9 (51) М. Кл.

Н 04Е 27/1Q

Н 03с 3/06 с присоединением заявкиГосударственный номнтет

Советв Мнннстров СССР оо делам изобретений и открытий (32) ПриоритетОпубликованЩ} ° О8,74Бюллетень № 32 (бз) удк 62I.376.

° 32(088.8) дата опубликования описания I5i 72 ° 74 (72) Авторы изобретения

Н.И.Мясоед, Ф.Г.Нйндиренко и В.Н.Забелин (71) Заявитель

ЧАСтстНЦИ МЬНИПХЫтОГ (54) 1

Изобретение относится к технике передачи данных, в частности к устройствам преобразования сигналов с частотной манипуляцией.

Известны частотные манипуляторы, содержащие последовательно соедйнвнные задающий генератор, формирователь характеристических частот и манипулятор, а также последовательно соединенные схему 1о

"ИЛИ", регистр сдвига, блок "весовых" коэффициентов и сумматор.

Недостаток таких манипуляторов состоит в том, что они не обесп8чиВают получения Выходного сигна- i5 ла заданной формы с достаточной точностью из-за- внутриаппаратурных искажений.

Цель изобрет8ния - снижени8 внУтРиаппаРатУРны» HGKQKSHEN H I10вышвние точности формирования выходного сигнала.

Эта цель достигается тем,что выходы промежуточных разрядов . м делителя частота манипулятора подключены через дешифратор к входам блока "мас1птабных" коэффициентов, а выход стар1пего разряда этого делителя подключен к управляющему входу коммутатора знака. к информационному входу которого подключен выход сумматора ; причем дешифратор выполнен в виде избиратель ной схемы, каждый выход которой подключен к парафазным входам двух тРИГГЕРОВе РаСПОЛОжЕННЫХ СИММЕтРИЧ. но относительно середины цепочки этих триггеров, через соответствующие схемы "И", к потенциальным входам которых подключены соответствующие парафазные выходы пред. последнего разряда делителя частоты манипулятора.

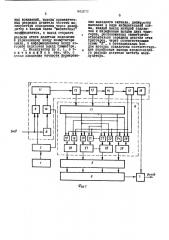

На фиг. 1 изображена блоксхема частотного aeasaymnoya ; на фиг. 2 — временная диаграмма, аоясняйцая работу манипулятора.

Манипулятор содержит задаю щийй генератор 1, формирователь 2

3 характерйстичвских частот, манипулятор 3 дешифратор 4, блок 5 "мас. штабных коаффипиентов, сукитор

6 и коммутатор 7 знака.

Последовательность имаульсов от задающего генератора Х поступает на формирователь 2, в котором аутем дискретного деления и суммирования Образуются частоты, KghTные в М раз нижней 7< и верхней 7, характеристическим! частотам. Полученные частоты поурются на ванипулятор 3, управляемый информационным сигналом, выходы которого аодключвны к двшифратору 4. Выходы двшифратора управляют блоком 5 "масштабных" коэффициентов, и через сумматор 6 "взвещенная" имаульсная последовательность поступает на информационный вход коммутатора 7 знака, осуществляющего формирование двухполярного сигнала, Частотный маниаулятор работает следующим Образом.

При поступлвнии информационного сигнала аоложительной аолярности (фиг. 2,а) на вход манипулятора 3 состоящего из инввртора 8, схем 4" 9,IQ "ИЛИРР П и разрядов I2-Хб Делителя, с выхода схемы

"ИЛИ" П поступают импульсы с частотой кратной У .

1азряды I2-16 делителя манипулятора подключены двшифратОру 4, состоящему из избирательной схемы

):7, логических схем "И" IB-25 и цвйачкй триггеров 26-29, Входы логических схем подготавлиеаются паОафазными выхОдами йрвдпослв вго разряда I5 делителя манийулятора 1фиг. 2 в). Выход схем "И" IB<20,22,24 включены на " яичные" входй, а выходы схем "И" I9,2I,23,35 — на "нулевые" вхОды цепочки триггеров, В рассматпивавмый момент открыты схемы "И IB„20,22,24 и под действием импульсов с выходов из бирательной схемы I7 триггеры

26-29 аослвдоватвльно устанавлиВВБь ся в состОЯние I фиг ф 2 р з р и,к). После становки триггера 2э

В состОЯние I прОисхОДИ изменение состояния разряда 1ь триггера) (фиг.2,в). Ops этом разрешавший потейцйал подается на схемы

" И" Ьр2I,23 25, выходы которых включвйы йа "a левые" входы цепоч ки триггеров, кл работы избираT8833338oN GxeeMMH I Q0aaTT0g88-ÿ, триггврн 26-29 в обратной последовательности аерввОдятся в состоя20

ПРЕДАДЕТ ИЗОБРЕТЕНИЯ

I. Частотный манипулятор, содержащйй на входе задааций гейвратор, управляемый маниаулятором с делйтелем частоты на его выходе через формирователь характеристических частот, а также аоследовательно совдинвнныв блок "масштабных" коэффициентов и сумматор, отличающийся тем, что, с целью снижения внутриаппаратур"О"

>HxeÞ e сигналы С цепочки три7геров двшифратора Циг, 2, з, ирк) Щоходят через блок 5 "масш табных . коэффициентов. Коэффициенты передачи по каждо из входов этого блока подобраны, исходя из требований получ8ния выходниГО сих нала заданной формы (в данном случае сигнала близкого по форме

К СИНуСОИдаЛЬНОму). С бЛОка 5, "взввшвнныерр сигналы линейно преобразуются сумматором 6, на выходе которого формируется однополярный сигнал, поступающий на коммутатор 7 знака. Коммутатор знака„ управляющий вход которого включвй к старшему разряду I6 двлителЯ манипУЛЯтоРа Зр измвнЯет полярносгь выходного сигнала в сОвтввтстэии с полярностью ущ)авляюцвго сигнала (фиг. 2, г).

РаССматРИВаВМЫй МОМВйт ВРЕМЕНИ на управляющий вход коммутатора 7 знака поступает высокий потенциал, и на вго выходе формируется положительный полупериод сигнала частоты Го., близкий по форме о синусоидальному (фиг. 2 л). После установки триггеров 26-29 в состоянив "О" ароисходит изменение состоя ния старшего разряда делителя, и на коммртатор нака поступает низкий потенциал (фиг. 2,г), на выходе которого формирувтся отрйцатвльый полупериод выходного колебания фиге 2 р.п. ) е

Прй йоступлвнии на вход манипулятора 3 сигнала отрицательной полярности на вход первого разряда делителя через Открытую схему

И" ТО поступают импулфсы МсТ0той, кратной 7z (фиг. 2,6).

Работа Остальных узлов айалогична работв при поступлении информационного сигнала положитвльнов полярности, но в этом случае на выходе коммутатора знака формируется двухполярный сигнал с частотой слвдования E> . ных искяпениИ, . выходы промеж точных разрядов делителя частоты манипулятора подклшчекы через дешифратор к входам блока "Масштабнйх коэффициентов, я выход старшего разряда этого делителя подключен н управляющему Входу коммутатора анака, к информационному входу которого подключен Выход сумматора, 2» Манипулятор по и, Х О Tл и ч я В щ ж И с я тем, что, с цельа аовыавния точности фоомировяния выходного caraana, деширр тор

ssaomea s 8 избирательной мы, кявдыИ выход котороИ подключей к паряфязным входам двух триг-. геров, рясполозенных симметрично относйтельно сврединй цепочки этих

ТРИГГ8ДОВн ЧЕР83 СООТЗЕТСТВУЕМЦИ8 схемы И", к потенциальным входам которйх подключены соответствую о Щие ПЯРЯфазные ВЫХОДЫ ПР8ДПОСЛЕДН8" го разряда делителя частоты мяни. ПУЛЯТОРЯ е

Заказ Ттт

Изд. И /ОГ Тираж g уЩ Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, I l3035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская иаб., 24

Составитель Н ggQQQQ

РедакторМ БЫЧКОВЫМ ТехредД фЦУЩ з ЩКорректор.1 .КИСЕЛЕВа