Устройство для обработки и передачи информации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 44247!

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 13.10.72 (21) 1838645/18-24 с присоединением заявки М (32) Приоритет

Опубликовано 05.09.74. Бюллетень М 33

Дата опубликования описания 04.07.75 (51) М. Кл. G 06f 7/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.3(088.8) (72) Авторы изобретения

В. П. Грибок, Ю. Н. Костин и Г. С. Анурьев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ И ПЕРЕДАЧИ

ИНФОРМАЦИИ

Изобретение относится к области телемеханики, в частности к устройствам для телеизмерений.

Известны устройства для передачи информации, содержащие блок сокращения избыточно- 5 сти, формирователь кода адреса, буферный запоминающий блок, блок синхронизации и блок управления формированием кода.

Недостатком таких устройств является низкая достоверность передаваемой информации 10 из-за отсутствия сведений о характере сокращения избыточности.

Целью изобретения является расширение области применения устройства.

Предложенное устройство дополнительно 15 содержит формирователь кода времени, состоящий из элемента задержки, реверсивного счетчика и трех двухкодовых схем «И». Объединенные первые входы первой и второй схем

«И» соединены с первым выходом блока уп- 20 равления формированием кодов, второй выход которого подключен к первому входу третьей схемы «И». Второй вход последней связан со вторым входом формирователя кода адреса и входом элемента задержки, выход которого 25 соединен со вторым входом первой схемы «И».

Второй вход второй схемы «И» подключен к первому входу буферного запоминающего блока, а выходы первой, второй и третьей схем

«И» подключены соответственно к суммирую- 30 щему, вычитающему и сбросовому входам реверсивного счетчика, выход которого соединен с управляющим входом блока сокращения избыточности.

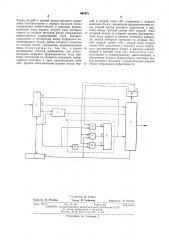

Схема устройства представлена на чертеже, где обозначено: 1 — блок синхронизации с первым выходом 2; 3 — блок сокращения избыточности; 4 — формирователь кода адреса;

5 — второй выход блока 1 синхронизации; 6— формирователь кода времени; 7 — буферный запоминающий блок; 8 и 9 — первый и второй выходы блока 3 сокращения избыточности;

10 — блок управления формированием кода с первым 11 и вторым 12 выходами; 13 — элемент задержки формирователя кода времени

6; 14 — двухвходовая схема «И» блока 6; 15— суммирующий вход реверсивного счетчика 16 блока 6; 17 — вторая двухвходовая схема «И» блока 6; 18 — вычитающий вход счетчика 16;

19 — третья двухвходовая схема «И» блока 6;

20 — сбросовый вход счетчика IG; 21 — управляющий вход блока 3.

В предлагаемом устройстве осуществляется кодирование времени по задержке информации в буферном запоминающем блоке, прямо пропорционально заполнению последнего. Задержка (3) информации, поступающей в буферный запоминающий блок, определяется количеством (C) заполненных в нем ячеек па442471 б0

3 мяти умноженным на период (Т) считывания информации из одной ячейки этого блока

З=С т.

Так как в подавляющем большинстве телеметрических адаптивных систем точность временной привязки не должна превышать нескольких периодов считывания, то достаточно передавать, какому промежутку (C,—:С;+Д соответствует заполнение перед записью инфоръгации на оуферный запоминающий блок, 1ipii этом временная привязка будет осуществлена с точностью до 1/2. (С;.г.г — C;) Т, Для того чтооы точность временной привязки была постоянной, достаточно разбить общее количество ячеек памяти буферного запоминающего блока с определенным количеством ячеек (С;) на равные части (С, г — С;=

=С;+г — С;) и передавать в качестве информации о времени номер участка разбиения. Для осуществления такого разбиения можно воспользоваться блоком управления формированием кода, который, дешифрируя заполнение буферного запоминающего олока, должен выдавать информацию об опустошении последнего и о заполнении в нем определенных количеств ячеек.

Устройство работает следующим образом.

Блок синхронизации 1 посылает первого выхода 2 тактовые импульсы управления блоками 3 и 4, а со второго выхода 5 сигналы считывания, управляющие работой блока б и определяющие частоту считываний из буферного запоминающего блока 7. Блок 3 определяет неизбыточные выборки и передает их с перного выхода 8 в буферный запоминающий блок 7. 11ри появлении неизбыточной выборки на втором выходе 9 блока 3 появляются сигналы, идущие на входы блоков 4 и б. Формирователь кода адреса 4 по сигналам блоков 1 и 3 формирует кодовые группы, отображающие номер канала, которому принадлежит неизбыточная выборка, и передает их в блок 7.

Блок 10 управления формированием кода реагирует на заполнение ячеек буферного загн минающего блока 7 неизбыточными выборками, ожидающими считывания: на первом выходе 11 разрешающий потенциал появляется при заполнении в блоке 7 любого из фиксированных количеств (С,) ячеек памяти, на втором выходе 12 разрешающий потенциал появляется при отсутствии в блоке 7 заполненных ячеек. Сигналы с выходов блока 10 управляют работой формирователя кода времени б.

Импульсы записи со второго выхода 9 блока 3 поступают на формирователь кода времени б, где подаются на элемент задержки

13 на время, достаточное для изменения сосостояния блока 10. Задержанный элементом

13 импульс поступает на вход первой двухвходовой схемы «И» 14 формирователя кода времени 6, на другой вход которой поступает потенциал с первого выхода 11 блока 10. Сигнал с выхода схемы «И» 14 поступает на сум5

4 мирующий вход 15 счетчика 16. Таким ооразом, содержимое счетчика 16 уве.гичивается на единицу после того, как в буферном запоминающем блоке 7 окажется заполненным неизоыточными выборками одно из фиксированных количеств 1С;) ячеек памяти.

Импульс считывания со второго выхода 5 блока синхронизации 1 поступает на буtpQpный запоминающий блок 7 и на схему «И» ! г, на другой вход которой поступает разрешающий потенциал с выхода 1! блока 10.

Сигнал с выхода схемы «И» 17 подается на вычитающий вход 18 счетчика !6. 1аким ооразом, если производится считывание из byферного запоминающего олока 7, в котором оыло заполнено неизбыточными выоорками одно из фиксированных количеств (С;) ячеек памяти, то содержимое счетчика 16 уменьшится на единицу, На схему «И» 19 поступают сигнал записи со второго выхода 9 блока 3 и потенциал со второго выхода 12 блока 10. 11отенциал на выходе 12 будет разрешающим при отсутствии в буферном запоминающем блоке 7 неизбыточных выборок, ожидающих считывания.

Сигнал с выхода схемы «И» 19 поступает на сбросовый вход 20 счетчика 16. Таким образом, сброс счетчика 16 происходит тогда, когда производится запись выборки в буферный запоминающий блок 7, все ячейки которого освобождены от неизбыточных выборок, ожидающих считывания. Такой сброс гарантирует правильную начальную установку содержимого счетчика 16 и позволяет исправлять отдельные возможные сбои в его работе.

Выходные сигналы счетчика 16 поступают на управляющий вход 21 блока 3 и на буферный запоминающий блок 7. Содержимое реверсивного счетчика отражает заполнение буферного запоминающего блока 7 перед записью выборки и в зависимости от содержимого счетчика 16 блок 3 меняет характер сокращения избыточности. Таким образом, содержимое счетчика 16 позволяет точно определить характер сокращения избыточности, производимого блоком 3. С другой стороны, содержимое счетчика определяет задержку информации в буферном запоминающем блоке

7 и является, таким образом, информацией о времени.

Применение предложенного устройства увеличивает достоверность передаваемых сообщений путем передачи с каждой неизбыточной выборкой информации о характере сокращения избыточности, которое было произведено.

Предмет изобретения

Устройство для обработки и передачи информации, содержащее блок сокращения избыточности, первый вход которого объединен с первым входом формирователя кода адреса и соединен с первым выходом блока синхронизации, второй выход которого подключен к первому входу буферного запоминающего

442471

Составитель В. Грибок

Техред В. Рыбакова

Корректор Л. Котова

Редактор Л. Утехина

Заказ 1341/1 Изд. № 457 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 5К-35, Раушская наб., д. 4, 5 типография, пр. Сапунова, 2 блока, второй и третий входы которого соединены соответственно с первым выходом блока сокращения избыточности и выходом формирователя кода адреса, второй вход которого связан со вторым выходом блока сокращения избыточности, управляющий вход которого подключен к четвертому входу буферного запоминающего блока, выход которого соединен со входом блока управления формированием кода, отличающееся тем, что, с целью расширения области применения, оно дополнительно содержит формирователь кода времени, состоящий из элемента задержки, реверсивного счетчика и трех двухвходовых схем

«И», причем объединенные первые входы первой и второй схем «И» соединены с первым выходом блока управления формированием кода, второй выход которого подключен к первому входу третьей схемы «И», второй вход

5 которой связан со вторым входом формирователя кода адреса и входом элемента задержки, выход которого соединен со вторым входом первой схемы, «И», второй вход второй схемы «И» подключен к первому входу буфер10 ного запоминающего блока, а выходы первой, второй и третьей схем «И» подключены соответственно к суммирующему, вычитающему и сбросовому входам реверсивного счетчика, выход которого соединен с управляющим входом

15 блока сокращения избыточности.