Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ((() 442512

Сон)з Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 02.10.72 (21) 1833987/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 05.09.74. Бюллетень № 33

Дата опубликования описания 10.04.75 (51) М. Кл. б llс 11/06

Государственный комитет

Ceeera министров СССР по делам иэобретений и открытий (53) УДК 681.32766 (088.8) (72) Авторы изобретения (71) Заявитель

В. М. Гриць и А. Н. Пресняков

Особое конструкторское бюро вычислительной техники

Рязанского радиотехнического института

1":. (54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств (ЗУ).

Известно логическое ЗУ, содержащее накопитель, выполненный на ферромагнитных сердечниках с прямоугольной петлей гистерезиса, входы которого соединены с выходами формирователей разрядных и адресных токов, а выходы — с усилителями считывания, регистр числа, входы которого подсоединены к выходам соответствующих схем «И», а выходы — к одним входам схем «И» и входам схем управления, подсоединенным к формирователям разрядных токов, и схемы задержки, подключенные к усилителям считыванияя.

Недостатком известного ЗУ является то, что оно содержит громоздкие и ненадежные элементы — схемы задержки.

Описываемое ЗУ отличается от известного тем, что оно содержит схемы «НЕ» по числу разрядов накопителя, входы которых подключены к выходам соответствующих усилителей считывания, а выходы — к другим входам схем «И».

Это позволяют упростить устройство и повысить надежность его работы.

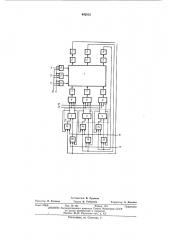

На чертеже показана структурная схема логического ЗУ, выполняющего логические операции «сумма по модулю два» и «логическая равнозначность» с образованием результата операций в ячейке памяти.

Оно содержит накопитель, выполненный по одной из схем 2Д или ЗД, усилители считывания 2, схемы «НЕ» 3 по числу разрядов, триггеры 4 регистра числа 5, схемы управления 6, формирователи разрядных токов 7, формирователи адресных токов 8, имеющие адресные входы 9.

10 Другие входы формирователей 8 подключены к управляющим шинам 10 и 11. Входы схем управления 6 подключены к управляющим шинам 12 и 13, «Нулевые» выходы триггеров 4 соединены с одними входами схем

15 «И» 14, а «единичные» вЂ” с одними входами схем «И» 15. Входы схем «НЕ» подключены к выходам усилителей считывания 2, а выходы — к другим входам схем «И» 14 и 15.

Третьи входы схем «И» 14 и 15 подсоедипе20 ны к управляющим шинам 16 и 17.

Устройство работает следующим образом.

При выполнении логической операции

«сумма по модулю два» выбранный формирователь 8 формирует импульс тока записи, а

25 формирователь 7 — ток запрета записи в тех разрядах, где триггеры 4 установлены в

«нуль». В результате действия адресных и разрядных токов в ячейке памяти накопителя 1 образуется результат поразрядной дизь30 юнкции двух слов: хранимого в ячейке памя442512 ти и записанного в регистр числа 5. При этом в выбранной ячейке памяти производится перемагничивание сердечников из нулевого состояния в единичное в тех разрядах, где в регистре числа 5 записана «единица», а в ячейке памяти накопителя 1 хранится «нуль».

Следовательно, на выходах усилителей считывания 2 возникают единичные сигналы, соответствующие поразрядной логической функции «запрет от У», а на выходах схем «НЕ»

3 — сигналы, соответствующие функции «импликация от Х к У». На входы схем «И» 14 подается синхросигпал по шине 1б, а на их выходах появляется сигнал, соответствующий поразрядной «конъюнкции» двух слов: хранимого в ячейке памяти и записанного в регистр числа 5. Код с выходов схем «И» 14 записывается в регистр числа 5.

В следующем такте осуществляется коррекция результата путем считывания в тех разрядах, где сигнал на выходах схем «И»

14 соответствовал логической «единице». Для этого формирователь 8 вырабатывает ток считывания, который поступает в выбранные адресные шины накопителя 1. В тех разрядах, где выходной сигнал схем «И» 14 «пулевой», считывание не производится, так как формирователи 7 в этом случае по сигналу, поступающему на шину 13, выдают в разрядные шины токи запрета считывания.

При выполнении операции «логическая равнозначность» в первом такте по сигналу на шине 10 формирователь 8, как и в первом случае, вырабатывает импульс тока записи, по формирователи 7 по сигналу па шипе 12 формируют импульсы тока запрета записи в тех разрядах, где триггеры 4 установлены в состояние «единица». В результате в ячейке памяти образуется код, соответствующий результату логической операции «импликация от Х к У», а на выходах усилителей считывания 2 — результат «операции Пирса». Единичный сигнал на выходах схем «НЕ» 3 соответствует дизыонкции одноименных разрядов слов: записанного в регистре 5 и хранимого в ячейке памяти. Эти сигналы подаются на входы схем «И» 15 и, при наличии сигнала

»а шине 17 с их выходов на входы триггеров 4.

Этот код является результатом конъюнкции отрицания переменной Х, хранящейся в регистре 5, и дизъюнкции переменных Х и У, т. е. «запрет по Х».

В следующем такте производится коррекция путем считывания в тех разрядах, где сигнал на выходах схем «И» 15 был равен

15 «единице», в остальных разрядах формируются токи запрета считывания, так как содер>кимое ячейки памяти является дизъюнкпи ей двух функций: «логическая равнозначность» и «запрет по Х» двух переменных.

Предмет изобретения

25 Логическое запоминающее устройство, содер>кащее накопитель, выполненный на ферромагнитных сердечниках с прямоугольной петлей гистерезиса, входы которого соединены с выходами формирователей разрядных и ад30 ресных токов, а выходы — с усилителями считывания, регистр числа, входы которого подсоединены к выходам соответствующих схем

«И», а выходы — к одним входам схем «И» и входам схем управления, подсоединенным

35 к формирователям разрядных токов, о т л ич а ю щ е е с я тем, что, с целью упрощения устройства и повышения надежности его работы, опо содержит схемы «НЕ» по числу разрядов накопителя, входы которых подключе40 ны к выходам соответствующих усилителей считывания, а выходы — к другим входам схем «И».

442И2 и

Составитель В. Рудаков

Техред В. Рыбакова

Редактор Л. Утехина

Корректор А. Дзесова

Типография, пр. Сапунова, 2

Заказ 926/8 Изд. № 453 Тираж 591 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5