Однородная вычислительная среда

Иллюстрации

Показать всеРеферат

с A:с ! ;Г

О П И С А — "Н "И"Й изовгитения (ii) 443382

Союз Советскнх

Соцналнстнческнх

Респ1сблнк

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61} Зависимое от авт. свидетельства (22) Заявлено 14.02.73 (21) 1884147118-24 (51) М. Кл. G 06f 7i 00 с присоединением заявки №

Государственный комитет (32) Приоритет

Опубликовано 15.09.74. Бюллетень № 34

Дата опубликования описания 12.04.75

Совета Министров СССР ио делам изобретений л открьстнй (53) УДК 681.325.65 (088.8) (72) Авторы изобретения

В. И. Потапов и В. Ф. Нестерук

Омский политехнический институт (71) Заявитель (54) ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА

Изобретение относится к области вычислительной техники.

Известны однородные вычислительные среды, содержащие матрицу структурно избыточных ячеек с перестраиваемыми функциональными блоками и блоки перестройки ячеек по числу строк матрицы, каждый из которых содержит рсгистры и коммутатор, входы которого соединены с выходами регистров.

Общим недостатком известных однородных вычислительных сред является относительно низкая функциональная .надежность.

В предложенной однородной вычислительной среде указанный недостаток в значительной мере устранен.

Это достигнуто тем, что каждая ячейка вычислительной среды содержит дополнительные схемы запрета, схему антисовпадения и разделительный диод. Выход индикатора отказов функционального блока .каждой ячейки с-й строки матрицы соединен со входом дополнительной схемы антисовпадения той же ячейки и через разделительный диод соединен

". i-й шиной индикации отказов, подключенной ко входам дополнительных схем антисовпадения vñåõ ячеек i-и строки матрицы и к управляющему входу коммутатора блока перестройки ячеек той же строки. Выход дополнительной схемы антисовпадения каждой ячейки соединен со входами всех дополнительных схем заспрета той жс ячейки, выходы которых соединены с управляющими входами перестрапваемого функционального блока ячейки.

Вторые входы /-х дополнительных схем запрета всех ячеек t-й строки матрицы соединены с .с-м выходом ком сyтaторa блока перестройки ячеек той же строки. Последний выход коммутатора соединен с клеммой индикации невосстанавливаемых отказов.

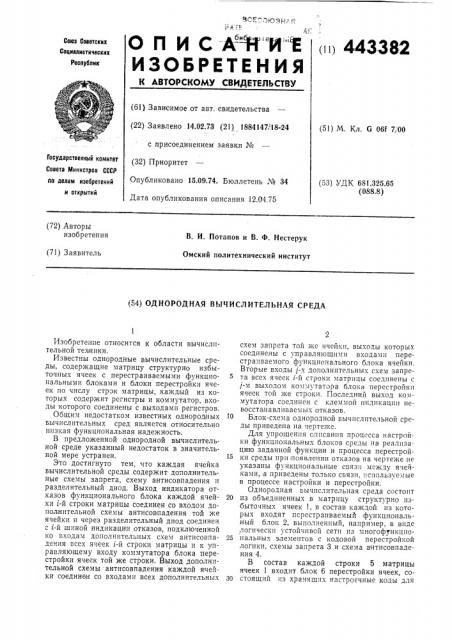

Блок-схема однородной вычислительной среды приведена на чертеже.

Для упрощения списания процесса настройки функциочальных блоков среды на реализацию заданной функции и процесса перестрой15 ки среды при появлении отказов на чертеже нс указаны функциональные связи между ячейками, а приведены только связи, .:спользуемые в процессе настройки и перестройки.

Однородная вычислительная среда состоит

20 из ооъединенных в матрицу структурно избыточных ячеек 1, в состав каждой из котоpbIx входят персстраиваемьпЪ функциональный блок 2, выполненный, например, в виде логически устойчивой сети из многофункцссо25 нальных элементов с кодовой перестройкой логики, схемы запрета 3 и схема антисовпадения 4.

В состав каждой строки 5 матрицы ячеек 1 входит блок 6 перестройки ячеек, со30 стоящий нз храчящ:сх настроечные коды для

443382

I0

25 перестройки блоков 2 регистров 7 (по числу циклов перестройки), необходимых для обеспечения логической устойчивости сети из многофункциональных элементов перестраиваемого функционального блока 2 любой ячейки

1 строки 5 в классе реализуемых функций, и коммутатор 8 выходов регистров 7. Выходы 9 каждого регистра 7 подключены к входным шинам 10 коммутатора 8, а входы 11 регистров 7 соединены с выходными шинами запоминающего устройства настроечных кодов функций, реализуемых ячейками 1 однородной вычислительной среды.

Каждый из выходов 12 коммутатора 8 подключен к функциональному входу 13 одной из схем запрета 3 каждой ячейки 1 соответствующей строки 5 однородной среды. Управляющие входы 14 схем запрета 3 каждой ячейки 1 соединены параллельно и подключены к выходу 15 схемы антисовпадсния 4, управляющий вход 1б которой соединен с выходом 17 индикатора отказов функционального блока 2.

Функциональный ьход 18 каждой схемы антисовпадения 4 подключен к шине 19 индикации отказов соответствующей строки 5 матрицы. Шина 19 каждой строки соединена через разделительные диоды 20 с выходами 17 индикаторов отказов перестрапваемых функциональных блоков 2 этой строки и подключена к управляющему входу 21 соответствующего коммутатора 8, а выходы 22 схем запрета 3 каждой ячейки 1 соединены с управляющими входами 23 соответствующего перестрапваемого функционального блока 2.

Сигналы, поступающие па управляющие входы 23 функционального блока 2, производят его настройку HB реализацию заданной функции.

Выход 24 коммутатора 8 каждой строки 5 подключен к клемме 25 индикации невосстанавливаемых отказов.

Если перед началом работы все ячейки 1 однородной вычислительной среды находятся в исправном состоянии, то процесс настройки любой строки 5 на реализацию произволной из класса реализуемых функций осуществляется следующим образом.

В регистры 7 блока б перестройки ячеек 1 каждой строки из за|поминающего устройства заносятся настроечные коды, обеспечивающие настройку на.заданную функцию, во всем диапазоне .логической устойчивости сетей из многофункциональных элементов перестраиваемых функциональных блоков 2 соответствующей строки 5 однородной вычислительной среды. Настроечные коды с выходов 9 регистров 7 поступают на входы 10 коммутатора

8, который пропускает на выходы 12 только код с первого регистра 7. Первым регистром считается тот, в котором хранится настроечный код, обеспечивающий логическую устойчивость функциональных блоков 2 к максимальному числу отказов, компенсируемых на одном настроечном коде. Следующие по порядку регистры 7 содержат настроечные козо

Ç5

65 ды, обеспечивающие убывающую способность функционального блока 2 к компенсации отказов. При этом совокупность всех настроечных кодов обеспечивает компенсацию в функциональном блоке 2 всех возможных отказов. Настроечные коды с выходов 12 коммутаторов 8 поступают на функциональные входы 13 схем запрета 3 каждой ячейки 1 соответствующей строки 5 вычислительной среды.

В связи с тем, что ячейки 1,,как было условлено, находятся в исправном состоянии, то сигналы на выходах 17 индикаторов отказов функциональных блоков 2 и в шине 19 индикации отказов каждой строки отсутствуют, и на управляющие 16 и функциональные 18 входы схем антисовпадения 4 поступают нулевые потенциалы. Это обуславливает отсутствие сигналов на выходах 15 схем антисовпадения 4 и на управляющих входах 14 схем запрета 3. Сигналы, поступающие на функциональные входы 13 схем запрета 3, беспрепятственно проходят на управляющие входы 23 перестраиваемых функциональных блоков 2 ячеек каждой строки 5 и производят настройку каждого блока 2 соответствующей строки на реализацию заданной функции.

Настроенные таким способом ячейки 1 однородной вычислительной среды функционируют без логической перестройки до тех пор, пока в одной из ячеек не .появится отказ, обнаруживаемый в зависимости отпринцппа построения среды либо аппаратурной системой контроля, либо с помошью тсстового контроля.

При обнаружении неисправности в функциональном блоке 2 строки 5, приводящей к искажению выходного сигнала, на выходе 17 соответствующего индикатора отказов появится сигнал об отказе. Этот сигнал поступает на управляющий вход 1б соответствующей схемы антисовпадения 4 и, проходя через разделительный диод 20, поступит в шину 19 индикации отказов соответствующей строки

5, на функциональные входы 18 всех схем антисовпадения 4 данной строки и на управляющий вход 21 коммутатора 8. По этому сигналу коммутатор 8 опрашивает следующий по порядку регистр 7, и на его выходы 12 поступает очередной настроечный код, который проходит на функциональные входы 13 схем запрета 3 всех ячеек 1 данной строки 5.

Схемы запрета исправных ячеек этой строки запираются, поэтому сигналы настроечного кода, поступающие на функциональные входы

13 схем запрета 3 исправных ячеек, не проходят на управляющие входы 23 перестраиваемых функциональных блоков 2 этих ячеек и не производят логической перестройки этих блоков. Логическая перестройка функцио нального блока 2 происходит лишь в той ячейке, в которой проявляется неисправность. приводящая к искажению выходного сигнала, так как только в этой ячейке схемы за443382 прета 3 открыты. На этом заканчивается первый цикл перестройки.

Если после первого цикла перестройки происходит компенсация отказа за счет логической .перестройки сети из многофункциональных элементов в функциональном блоке

2 неисправной ячейки 1, то сигнал на выходе

17 индикатора отказов |функционального блока 2 этой ячейки отсутствует. Это вызывает появление сигнала на выходе 15 соответствующей схемы антисовпадения 4 (при наличии единичного сигнала в шине 19 индикации отказов .данной строки 5), который поступает на управляющие входы 14 схемы запрета 3 и запирает схемы рассматриваемой ячейки, что делает невозможным логическую перестройку сети из многофункциональных элементов соответствующего функционального блока 2 в последующих циклах процесса перестройки. Наличие единичного сигнала в шине 19 индикации отказов соответствующей строки 5 после окончания первого цикла перестройки указывает на то, что в этой строке находится ячейка, оставшаяся неисправной после первого,цикла перестройки. В связи с этим начинается второй цикл перестройки.

По сигналу, поступающему на управляющий вход 21 коммутатора 8 по шине 19 соответствующей строки, коммутатор 8 опраши.вает очередной регистр 7, и на выходах 12 .коммутатора появляются сигналы очередного ,настроечного кода, которые проходят через открытые схемы запрета 3 оставшейся неисг.:ðàBíoé ячейки 1 этой строки и производят логическую перестройку функционального блока 2 этой ячейки.

В дальнейшем второй цикл перестройки протекает аналогично предыдущему. ,Процесс перестройки с целью компенсации отказа содержит столько циклов, сколько требуется для восстановления исправного функционирования отказавшей ячейки. Признаком окончания перестройки (восстановления отказавшей ячейки) является отсутствие сигналов в шине 19 индикации отказов.

Предложенный способ перестройки обеспечивает возможность одновременного устранения отказов в нескольких ячейках одной или нескольких строк однородной вычислительнои среды.

Если не происходит восстановление ис5 правного функционирования отказавших ячеек 1 какой-либо строки 5 после их перестройки настроечным кодом, хранящемся в последнем регистре 7 блока 6 данной строки, то на клемме 25 индикации невосстанавливаемых

l0 отказов соответствующего коммутатора 8 появится сигнал о невосстанавливаемом отказе.

Предмет изобретения

Однородная вычислительная среда, содержащая матрицу структурно избыточных ячеек с перестраиваемыми функциональными блоками и блоки перестройки ячеек по числу строк матрицы, каждый из которых содержит регистры и коммутатор, входы которого соединены с выходами регистров, о т л и ч а ющ а я с я тем, что, с целью повышения функ25 циональной надежности, каждая ячейка содержит дополнительные схемы запрета, схему антисовпадения и разделительный диод, выход индикатора отказов функционального блока каждой ячейки i-й строки матрицы со30 единен со входом дополнительной схемы ан исовпадения той же ячейки и через разделительный диод соединен с i-й шиной индикации отказов, подключенной к входам дополнительных схем антисовпадения всех ячеек -й

35 строки матрицы и к управляющему входу коммутатора блока перестройки ячеек той же строки, выход дополнительной схемы антисовпадения каждой ячейки соединен со входами всех дополнительных схем запрета той

40 же ячейки, выходы которых соединены с управляющими входами перестраиваемого функционального блока ячейки, вторые входы j-x дополнительных схем запрета всех ячеек i-H строки матрицы соединены с у-м выходом

45 коммутатора блока перестройки ячеек той же строки, последний выход коммутатора соединен с клеммой индикации певосстанавливаемых отказов..-..443382!

1

° °

° ° °

Составитель В. Потапов

Техред Н. Куклина

Корректоры: Л. Котова и Л. Брахнина

Редактор Е. Семанова

Типография, пр. Сапунова, 2

l5

I

11 1

1 (t

I

l

Заказ 778/2 Изд. № 1123 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5