Устройство микропрограммирования вычислительных машин

Иллюстрации

Показать всеРеферат

О П И И-"ЕИЗОБРЕТЕНИЯ

-- п 443387

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИ,ЦЫТЕЙЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 21.01.72 (21) 1742185/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15.09.74. Бюллетень № 34

Дата опубликования описания 23.06.75 (51) М. Кл. G 06f 9/16

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.326(088.8) ((2) Авторы изобр гения (71) Заявитель

А. Н. Гегамов и С. Л. Гегамова

Тбилисский научно-исследовательский институт приборостроения и средств автоматизации (54) УСТРОЙСТВО МИКРOI1t Oi РАММйРОьАНИЯ

ЬЫ«1 И(ЛИ i L!,ËÜ iiÛÕ МАШИН

Изобретение относится к области вычислительной техники и может применяться в устройствах управления вычислительных машин.

Известны устройства микропрограммирования вычислительных машин, содержащие триггера, дешифратор, собирательные схемы и схемы совпадения.

Однако известные устройства обладают малым быстродействием. вызванным последовательным выполнением микроопераций.

С целью повышения быстродействия в предлагаемое устройство введен (и+1) дополнительный триггер (где n — целое положительное число), вторые входы ) схем «И» соединены с выходом первой дополнительной схемы «И», первый вход которой подключен к нулевому выходу (и+1) -ro триггера, а второй — к выходу генератора синхроимпульсов, а первые входы дополнительных i схем «И», вторые входы которых соединены соответственно с единичными входами т триггеров, подключены к выходу второй дополнительной схемы «И», первый вход которой соединен с единичныи выходом (а+1) -го триггера, а второй вход — с выходом генератора синхроимпульсов и с первыми входами и схем «И», вторые входы которых связаны соответственно с единичными выходами и дополнительных триггеров.

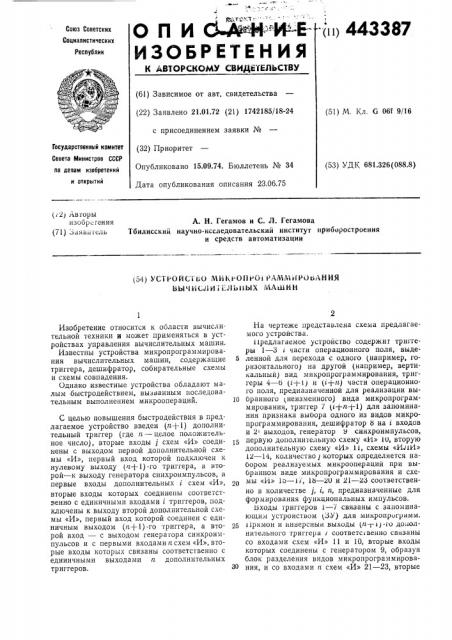

На чертеже представлена схема предлагаемого устройства.

11редлагаемое устройство содержит триггеры 1 — 3 i части операционного поля, выде5 ленной для перехода с одного (например, горизонтального) на другой (например, вертикальный) вид микропрограммирования, триггеры 4 — 6 (i i) и (т+и) части операционного поля, предназначенной для реализации вы10 бранного неизменного) вида микропрограммирования, триггер 7 (i+n+1) для запоминания признака выбора одного из видов микропрограммирования, дешифратор 8 íà i входов и 2 выходов, генератор 9 синхроимпульсов, первую дополнительную схему «И» 10, вторую дополнительную схему «И» ii, схемы «И И»

12 — 14, количество ) которых определяется набором реализуемых микроопераций при выбранном виде микропрограммирования и схемы «И» 1б — >i, 18 — 20 и 21 — 23 соответственно в количестве ), i, n, предназначенные для формирования функциональных импульсов.

Ьходы триггеров i — 7 связаны с запоминающим устроиством (ЗУ) для микропрограмм. !рямои и инверсныи выходы (и--т-г)-го дополнительного триггера соответс"венно связаны со входами схем «И» 11 и 10, вторые входы которых соединены с генератором 9, образуя блок разделения видов микропрограммироваЗ0 ния, и со входами и схем «И» 21 — 23, вторые

443387 с. Е . ° входы которых связаны соответственно с единичными выходами и триггеров 4 — 6. Выходы

i триггеров 1 — 3 подключены ко входу дешифратора 8, выходы которого через схемы

«ИЛИ» 12 — 14 связаны соответственно со входами j схем «И» 15 — 17, другие входы которых соединены с выходом первой дополнительной схемы «И» 10, Единичные выходы 1 триггеров 1 — 3 связаны со входами i схем «И»

1b — 20, вторые входы которых соединены с выходом второй дополнительной схемы «И» 11.

Работа устройства микропрограммирования происходит в следующей последовательности: в начале каждого рабочего такта процессора из ЗУ микропрограмм выбирают очередную микрокоманду, операционное поле которой запоминают на триггерах 1 — 7, управляющих схемами «И» 18 — 23 и дополнительными схемами «И» 10 и 11, а также через дешифратор 8 и схемы «ИЛИ» 12 — 14, схемами «И»

15 — 17. В каждом такте синхроимпульс поступает на входы схем «И» 21 — 23 независимо от признака выбора вида микропрограммирования, на входы схем «И» 19 — 20 — через схему «И» 11, когда триггер 7 находится в единичном состоянии, и на входы схем «И»

15 — 17, когда триггер 7 находится в нулевом состоянии.

Таким образом, на выходе схем «И» 15 — 23 формируют систему функциональных импульсов, соответствующих всем учтенным видам микропрограммирования.

Предмет изобретения

Устройство микропрограммирования вычислительных машин, содержащее i триггеров

5 (где i — целое положительное число), единичные и нулевые выходы которых соединены со входами дешифратора, выходы которого подключены к jсхе,мам «ИЛИ» (где 1 — целое положительное число), выходы которых соединены соответственно с первыми входами ! схем «И», вторые входы которых объединены, и генератор синхроимпульсов, о тл ича ющ е е с я тем, что, с целью повышения быстродействия, в него введен (и+1) дополнительный триггер (где n — целое положительное число), вторые входы ) схем «И» соединены с выходом первой дополнительной схемы «И», первый вход которой подключен к нулевому выходу (и+1)-го триггера, а второй — к выходу генератора синхроимпульсов, а первые входы дополнительных i схем «И», вторые входы которых соединены соответственно с единичными выходами i триггеров, подключены к выходу второй дополнительной схемы

«И», первый вход которой соединен с единичным выходом (и+1)-го триггера, а второй вход — с выходом генератора синхроимпульсов и с первыми входами п схем «И», вторые входы которых связаны соответственно с единичными выходами п дополнительных триггеров.