Устройство задержки аналогового сигнала

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОЯСКОМУ СВИДИТЕПЬСТВУ

< > 443471

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства— (22) Заявлено 12.01.73 (21) 1878654/26-9 с присоединением заявки №вЂ” (32) Приоритет—

Опубликовано 15.09.74. Бюллетень ¹ 34

Дата опубликования описания 12,08.75 (51) М. Кл. Н 03k 5/13 б 06д 7/02

Государственный комитет

Совета Министров СССР оо делам изооретений и открытий (53) УДК 681.337 (088.8) (72) Авторы изобретения

P. В. Коровин и В. В. Баканов (71) Заявитель (54) УСТРОЙСТВО ЗАДЕРЖКИ АНАЛОГОВОГО СИГНАЛА

Изобретение может найти применение при создании специализированных блоков вычислительных устройств.

Известны устройства для задержки аналогового сигнала, содержащие интеграторы на магнитных элементах, входы которых через ключи записи и блок размножения сигнала соединены с источником аналогового сигнала, а через ключи считывания — с источником напряжения считывания, в которых ключи записи и ключи считывания через соответствующие коммутаторы записи и считывания и вентили, управляемые триггерами записи и считывания, подключены к генератору тактовых импульсов, триггер записи соединен с источником сигнала записи непосредственно, триггер считывания — через блок регулируемой задержки, выходы интеграторов через сумматор и триггер Шмидта соединены с выходом устройства.

С целью обеспечения изменения временного масштаба задерживаемого аналогового сигнала в предлагаемом устройстве входы коммутаторов записи и считывания соединены с выходами вентилей через делители частоты.

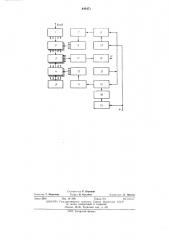

На чертеже изображена функциональная схема предлагаемого устройства задержки аналогового сигнала.

Устройство содержит блок размноже2 ния 1, на вход которого поступает задерживаемый аналоговый сигнал, разделяющийся затем на и аналогичных сигналов без изменения мгновенных значений. Каждый из спг5 палов поступает на свой выход блока размножения 1, который подключен к потенциальному входу ключей 2 записи, выходы последних, в свою очередь, подключены ко входам интеграторов 3 на магнитных элементах с

1о прямоугольной петлей гистерезиса.

К другим входам интеграторов 3 через ключи 4 считывания подключен источник 5 постоянного напряжения считывания У„.„.

Управляющие входы ключей записи 2 через

l5 коммутатор записи 6, делитель 7 частоты с изменяемым коэффициентом деления и вентиль 8 соединены с выходом генератора 9 тактовых импульсов, с которым через последовательное соединенные вентиль 10, дели20 тель 11 частоты с изменяемым коэффициентом деления и коммутатор 12 считывания соединены ключи 4 считывания. Управляющий вход вентиля 8 подключен через триггер записи 13 ко входу 14 сигнала «Начало

25 операции», который через блок 15 регулируемой задержки и триггер 16 считывания подключен к управляющему входу вентиля 10.

Выходы интеграторов 3 через сумматор 17 и триггер 18. Шмидта подключены к выхоз0 ду 19 устройства.

Задержка аналогового сигнала на заданный период тз и изменение его временного масштаба осуществляются следующим образом.

В исходном положении триггеры 13 и 16 и коммутаторы 6 и 12 находятся в положении, прн котором ключи 2 и 4 и вентили 8 и 10 закрыты, а интеграторы 3 — в нулевом состоянии. В блоке регулируемой задержки выставляется требуемое время задержки, а с помощью изменения коэффициентов деления делителей 7 и 11 устанавливается требуемый коэффициент изменения временного масштаоа задерживаемого сигнала.

В необходимьш момент времени на вход 14 поступает сигнал на начало операции задержки, воздействующий на триггер 13 записи, который открывает вентиль 8; на коммутатор 6 записи через вентиль 8 и делитель 7 частоты начинают поступать импульсы с генератора 9 тактовых импульсов.

В течение интервала времени между первым и вторым импульсами коммутатор держит открытым первый ключ записи, и входной аналоговый сигнал интегрируется первым интегратором 3. В интервале между вторым и третьим импульсами открыт второй ключ 2 записи, а очередная часть аналогового сигнала интегрируется вторым интегратором 3 и так далее, Изменение периода следования тактовых импульсов с помощью делителя 7 приводит к соответствующему изменению масштаба записанного сигнала.

По истечении времени тз после появления па входе 14 сигнала «Начало операции» появляется сигнал на выходе блока 15 регулируемой задержки, который воздействует на триггер 16 считывания, последний, открывая вентиль IO, направляет тактовые импульсы с генератора 9 через вентиль 10 и делитель 11 па коммутатор 12 считывания. Коммутатор 12, аналогично коммутатору 6, открывает поочередно на время интервала между тактовыми импульсами ключи 4 считывания, в результате чего напряжением с источника 5 осуществляется преобразование записанной в интеграторах 3 информации во времен443471

4 ные интервалы в соответствующем масштабе времени, поступающие на сумматор 17. На выходе сумматора 17 получается серия импульсов, длительность которых пропорциоБ нальна средним значениям входного сигнала за интервалы между тактовыми импульсами.

Широтно-модулированные импульсы с выхода сумматора нормализуются по амплитуде в триггере 18, с выхода которого они поступаlo ют на выход 19 устройства.

При изменении коэффициента деления делителя 7 в канале записи изменяется частота следования тактовых импульсов, что приводит к изменению временного масштаба за15 держиваемого сигнала. При изменении коэффициента деления делителя 11 в канале считывания изменяется временной масштаб считываемого сигнала. При одновременном изменении коэффициентов деления делителей 7

2о и 11 изменяется временной масштаб задержанного сигнала в произвольном отношении к реальному масштабу времени.

Предмет изобретения

Устройство задержки аналогового сигнала, содержащее интеграторы на магнитных элементах, входы которых через ключи запизо си и блок размножения сигнала соединены с источником аналогового сигнала, а через ключи считывания — с источником напряжения считывания, в которых ключи записи и ключи считывания через соответствующие з; коммутаторы записи и считывания и вентили, управляемые триггерами записи и считывания, подключены к генератору тактовых импульсов, триггер записи соединен с источником сигнала записи непосредственно, триггер

40 считывания — через блок регулируемой задержки, выходы интеграторов через сумматор и триггер Шмидта соединены с выходом устройства, отличающееся тем, что, с целью обеспечения изменения .временного масштаба

4„-. задерживаемого аналогового сигнала, входы коммутаторов записи и считывания соединены с выходами вентилей через делители частоты.

443471

Составигель Р. Коровин

Текред Н. Куклина

Редактор Т. Морозова

Корректор Л. Орлова

МОТ, Загорский филиал

Заказ 2б43 Изд. № 1091 Тираж 811 По гппсно

ЦНИИИ11 Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 4/5