Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i) 443482

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 31.05.71 (21) 1661160/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 15.09.74. Бюллетень № 34

Дата опубликования описания 08.04.75 (51) М. Кл. Н OSk 13/20

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.325(088.8) (72) Авторы изобретения

Г. О. Паламарюк, Н. И. Иона и В. Н. Соломаха (71) Заявитель

Рязанский радиотехнический институт

Бд Г -. (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД

Изобретение относится к области вычислительной техники, где может быть использовано в качестве входного преобразователя информации для .цифровых, вычислительных машин,,в качестве самостоятельного узла — частотомера, в качестве составной части частотно-импульсных вычислительных устройств.

Известен преобразователь частоты в код, содержащий устройство синхронизации, выходом соединенное с одним входом схемы сравнения, схемы совпадения, ревврсивный счетчик, выходы разрядов которого подключены ко входам двоичного умножителя.

В предложенный преобразователь введена схема коммутации частот и счетчик, вход которого соединен с выходом двоичного умножителя, а выход — со вторым входом схемы сравнения, выходы которой через схемы совпадения соединены со входами реверсивного счетчика,,вторые, входы схем совпадения подключены к выходам схемы коммутации частот, д ругими входами соединенной с шинами счетчика. Такое выполнение преобразователя позволяет павысить его быстродействие.

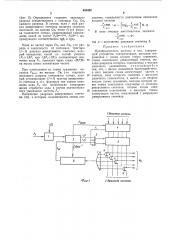

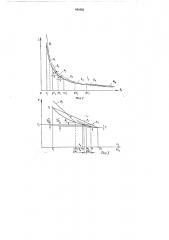

На фиг. 1 приведена схема преобразователя частоты в код; на фиг. 2 — кусочно-линейная аппроксимация гиперболической за висимости; на фиг. 3 — график, иллюстрирующий процесс отработки точного значения кода; нл фиг. 4 — схема сравнения и временные диаграммы, поясняющие ее работу; на фиг .5— схема коммутации частот.

Предлагаемый преобразователь частоты в код состоит из устройства 1 синхронизации, схемы 2 сравнения, схем 3, 4 совпадения, реверсивного счетчика 5, схемы 6 коммутации частот, схемы 7 сборки, счетчика 8.

Вход устройства F„÷åðåç устройство 1 синхронизации соединен со схемой 2 сравнения, на второй вход которой поступают импульсы частоты Р„cо счетчика 8. Выход «Сброс» схемы сравнения 2 подключен ко входу счетчика 8, выход F@ppp — ко входу схемы 6,коммутации частот, а выходы+ЛТ и — ХТ вЂ” к ino15 тенциальным входам двух импульсно-потенциальных схем 3 совпадения, импульсные входы которых соединены с выходом F> схемы 6 коммутации частот. Выходы импульсно-потенциальных схем 3 совпадения соединены с суммирующим и вычитающим входами,реверси вного счетчика. К роме того, единичные выходы ды триггеров реверсивного счетч ика 5 подключены ко входам схемы 6 коммутации частот, соединенной с,разрядами рвве рсивного опорных частотных составляющих Fp/2 с де. лителя частоты (Fp — опорная частота), а вы ходами для форсирования — с установочны ми единичными входами триггеров реверсивного счетчика 5. Единичные и нулевые выхо30 тригге ро в реверсивного счетчяка подключены

443482

10 к потенциальным;входам импульсно-потенциальных схем 4 совпадения, импульсными входами соединенных с шинами опорных частотных составляющих с делителя частоты и выходами подключенных ко входам схемы 7 сборки. Выход схемы сборки, подключен ко входу счетчи ка 8, с .выхода которого выдаются импульсы Р«на схему 2 сравнения.

Принцип действия предлагаемого преобразователя основан на сравнении периода входной частоты T„c пер иодом ча стоты связи Т«, начало которого синхронизи руется,импульсами частоты F и формировании ia случае их неравенства коррекции кода

ДИ„= ATÄ. F/, уточняющей его значение N, накапливаемое в выходном регистре, ЬТ„= T — T

F — частота, значение которой соответствует наклону /-го линейного участка аппроксимирующей кривой, k — шаг коррекции,,количество которых определяется точностью преобразования.

В предлагаемом преобразователе осуществляется кусочно-линейная аппроксимация ги1 перболической зависимости (фиг. 2) T„=—

Fx и .измеряемый период .или разность ЛТ заполняется импульсами, частоты которых дискретно изменяется в зависимости от получаемого кода ia моменты, соответствующие узлам апи р окси маци.и.

Узлы аппроксимации расположены в точках

F<, 2Рь 4I < ...,которым соответствуют следующие значения кодов N„ОО ... 001, 00 ... 010, 00 ... 0100, .... При этом значении тангенсов углов наклона tga, отрезков А;, проведенных через эти углы аппорксимации (фиг. 2), соответствуют ряду 1/2 > (j — 1, 1, 2, 3 ... n, n — количество участков аппроксимации) .

Для ускорения отработки результирующего кода каждый участок разделен на две части (Р,—:1,5F; и 1,5F; 2F;) и iB первых из них для выработки коррекции, используются прямые В;, проведенные из середины:каждого участка (1,5 F>, ЗРь 6Рь ... с соответствующими значениями кода 00 ...011, 00 ... 0110, 00;..01100, ...), а во вторых — прямые А;. Значения тангенсов угла наклона, прямых В, соответствуют ряду 1/2 / — .

Величины tga,, tgP; моделируются опорными частотными составляющими (Fo/2 — ;

Ро/2 — 0 — <)) .

Использование аппроксимирующих прямых

А; и В; на каждом участке позволяет простыми средствами, вычислить коррекцию

ЬИ„== ЬТ„ tg, p/($>)

-(фиг. 3) и за .несколько шагав коррекции (k)

-получить значение, кода N„c точностью, îïðåделяемой разрядной сеткой, 15

Частота Р„ через схему 1 синхронизаций поступает на вход схемы 2 сравнения, где осуществляется сравнение периодов измеряемой частоты T„c периодом частоты обратной связи Т«. Период Т«образуется путем п ростого деления импульсов неравномерной частоты двоичного умножителя счетчиком 8.

Д воичный умножитель преобразует код Л/„, накапливаемый реверсивным счетчиком 5, в о частоту F — N»,, которая в 2 " (где

2:с и — количество разрядов счетчиков 5 и 8) больше частоты обратной связи Fp сра вниваемой с частотой Р„в схеме сравнения 2.

Синхронизация периодов Т„и Т«, необходимая при сравнении, достигается путем начальной установки счетчика 8 импульсами частоты FÄÄ. Если Т„АТОС, то схема сравнения формирует соответствующие сигналы разности +ЬТ и — AT, ia течение времени существования которых на счетчик 5 поступают через схемы совпадения 3 импульсы частоты Р; со схемы 6 коммутации частот; которая определяет соответствующую частоту (Fp/2" — >, или

Fo/2" — О+" >, моделирующую tga; или tgP;.

В .результате последовательного сравнения периодов Т„и Т«на вход счетчика 5 поступают коррекци,и

ANÄ ATÄ.tg.,(I J) уточняющие значение кода N, до момента наступления pBiBBHcTва периодов T„= T ñ точностью, определяемой разрядной сеткой преоб разавателя.

11ри скачкообразном увеличении частоты F„ больше чем в 2 раза, схема сравнения 2,выдает,в схему 6 коммутации частот импульсы частоты Рф,р„,которые форсируют увеличение кода N„. в реверсивном счетчике 5.

Работа схемы сравнения, поясняется фиг. 4 (a, б), где Cn — Сп7 схемы совпадения, а Т, T2 — триггеры. Импульсы F«, совпадающие с импульсами F„(изображены пунктиром), соответствуют моментам синхронизации

«Сброс», т. е. началу сравнения периодов Т„ ,и Т«(фиг. 4б). Разность периодов +ЛТ образуется на выходе Сп, а — ЛТ вЂ” на выходе

Спб.

Схемы Сп> Сп4 — (И вЂ” НЕ) учаспвуют в формировании исходного состояния триггеров перед сравнением (Т вЂ” э«1», Т2 «0»). Сп< запрещает прохождение импульсов частоты F„„ в момент форм ирования +ЬТ, которые могут иметь место при скачкообразном увеличении частоты Р„больше чем в 2 раза. В этом случае,импульсы частоты Р„проходят через Спт и подаются на схему 6 коммутации частот для форсирования переходного п роцесса (Рф,р,).

Работа схемы коммутации частот поясняется фиг. 5, где Cn — Спз схемы совпадения, Т вЂ” Т вЂ” триггеры.

Участок аппроксимации (j). на котором находится значение F„, определяется ста ршим значащим разрядом реверсивного счетчика

443482

l дРЛаяРлй чоспю пы

Г denumene частоты (фиг. 2) . Определение старшего значащего разряда осуществляется с помощью Сп, Сп3 каждого разряда. В случае, если j- ный разряд реверсивного счетчика является старшим значащим, на выходе Спз этого (j-го) разряда появляется сигнал, раз решающий прохождение одной из частот Рс/2» — О+ >, F,/2 —, модулирующих соответственно tgP; и tgo.;.

Одна из частот через Сп4 или Спи j-го разряда в зависимости от состояния триггера (j — 1) разряда реверсивного счетчика, который определяет, какой,из частей участка (F; —:1,5F; или 1,5F; —:2F;) соответствует значению кода N„, проходит через схему «ИЛИ» на выход схемы коммутации частот.

При поступлении со схемы сравнения импульса буфорс, на выходе Cn< j-го старшего значащего раз ряда появляется сигнал, который устанавливает (i+/) триггер,реверсивного счетчика в «1», форсируя тем самым изменение кода У„что значительно сокращает цремя отработки кода в случае скачкообразного увеличения частоты F.„„.

Количество разрядо в реверсивного счетчика (т), к которым подкл|очаются схемы совпадения, определяется диапазоном изменения входной частоты с макс . 1о а. макс

F.

:т=

F,. „,tH .с мии

В свою очередь максимальное значение

F. х макс Оп — з

F» мии где и — количество разрядов счетчика 5.

Предмет изобретения

Преобразователь частоты в код, содержащий устройство синхронизации, выходом соединенное с одним входом схемы сравнения, 15 схемы совпадения, реверсивный счетчик, выходы 1разрядов которого подключены к входам двоичного умножителя, отличающийся тем, что, с целью повышения быстродействия. в,него введена схема коммутации частот и

20 счетчик, вход которого соединен с выходом двоичного умножителя, а выход — со вторым входом схемы сравнения, выходы которой через схемы совпадения соединены со входами реверсивного счетчика. вторые входы схем

25 совпадения подключены к выходам схемы коммутации частот, соединенной с разрядами реверсивного счетчика, 443482.с4юг"

Фиг га/

Редактор Н. Коган

Корректор Л. Котова

Заказ 693/8 Иэд. № 1107 Тираж 811 Подписное

;ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, и р. С а пуков а, 2

Т2

isa

Составитель Е. Семенова

Техред Т. Миронова