Десятичный счетчик импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАН ИЕ

ИЗОБРЕТЕН Ия

011 443486

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Зависимое от авт. свидетельства (22) Заявлено 23.01.73 (21) 1879261/26-9 с присоединением заявки ¹ (32) Приоритет

Опубликовано 15.09.74. Бюллетень ¹ 34

Дата опубликования описания 28.03.75 (51) М. Кл. Н 03k 23/08

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.382(088,8) (72) Авторы изобретения P. В. Васюткин, В. К. Кишенков, H. H. Косырев и К. П. Тимошенко (71) Заявитель (54) ДЕСЯТИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ

Предлагаемое изобретение относится к пересчетным схемам, выполненным на ферритполупроводниковых элементах автоматики и электроники.

Известны десятичные счетчики импульсов с регулируемым коэффициентом пересчета, выполненные на основе последовательных рсгистров сдвига.

Однако известные счетчики сложны, так как каждый его десятичный разряд должен состоять из десяти ячеек, при этом такие последовательные схемы большой длины имеют низкую помехозащищенность.

С целью повышения надежности устройства выходы дешифратора подключены к продвигающим обмоткам последовательного регистра и обмоткам гашения рекуррентного регистра через ячейки памяти, выход которых соединен через собственную линию задержки с ее входом, вход повторного запуска рекуррентного регистра соединен с его обмотками гашения через линию задержки, выход переключателя каждого старшего разряда через блок переноса соединен с входами записи ячейки памяти и блока переноса последующего младшего разряда, а через линию задержки — с нулевым входом переключателя последующего младшего разряда, выходы всех блоков переноса соединены непосредственно с обмотками гашения ячеек последовательного регистра и через линию задержки — с входом записи его первой ячейки, а выход блока переноса низшего разряда подсоединен непосредственно к входу записи блока переноса первого старше5 го разряда, и через линию задержки — к нулевому входу переключателя этого разряда.

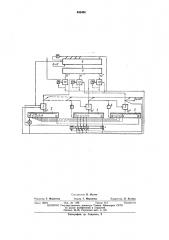

На чертеже показано предлагаемое устройство.

Десятичный счетчик импульсов содержит ре1О гистр 1 сдвига, переключатели 2 коэффициента пересчета, блок 3 переноса, линии задержки 4 — 7, дешифратор 8, рекуррентный регистр

9 и ячейки памяти 10.

Устройство работает следующим образом.

15 С помощью переключателей 2 устанавливается требуемый коэффициент пересчета в десятичном исчислении.

От отдельного устройства, не показанного на чертеже, производится подготовка счетчп20 ка к функционированию. Для этого, например, вручную с помощью кнопки одиночный импульс подготовки записывается в первые ячейки соответственно последовательного и рекуррентного регистров 1 и 9 сдвига, а также в

25 блок 3 переноса и ячейку памяти 10 старшего (левого по схеме) разряда. Далее все операции производятся автоматически.

Импульсы, подлежащие счету, подаются на вход счетчика в качестве считываемых на

30 все ячейки рекуррентного регистра 9. На со443486

3 ответствующих выходах дешифратора 8 последовательно появляются импульсы, коэффициенты пересчета которых по отношению к входным равны соответственно: 10", 10"

101 100 (= 1)

На выходе ячейки памяти 10 старшего разряда появляется сигнал, который поступает на обмотки считывания ячеек последовательного регистра 1, а так как импульс подготовки записывается в его первую ячейку, то происходит сдвиг сигнала в cro вторую ячейку. Одновременно этот же сигнал поступает на обмотки гашения рекуррентного регистра 9, произведя сброс всех его ячеек в нулевое состояние и повторную запись в его первую ячейку через линию задержки, которая задерживаег импульс записи на время, необходимое для надежного гашения сигналов во всех ячейках рекуррентного регистра 9. Кроме того, с выхода ячейки памяти 10 сигнал подготовки через линию задержки 5 переписывается на ее вход записи.

Следующая серия входных импульсов вновь вызывает срабатывание ячейки памяти 10 старшего разряда, гашение рекуррентного регистра 9 и продвижение сигнала на следующую (вторую) ячейку последовательного регистра 1, при этом сигнал с выхода этой ячейки через соответствующий (второй) вход переключателя 2 производит считывание с блока

3 переноса старшего разряда. Сигнал с его выхода производит подготовку к срабатыванию ячейки памяти 10 следующего разряда путем записи импульса на ее вход.

Одновременно сигнал с выхода блока 3 переноса старшего разряда производит подготовку к работе следующего младшего разряда путем подачи сигнала на вход записи блока переноса этого разряда и гашение всех ячеек последовательного регистра 1. Через линию задержки 7 производится подготовка к поворотному функционированию (на следующем десятичном разряде) последовательного регистра 1 путем записи сигнала в его первую ячейку.

Следующий цикл состоит в том, что после прохождения на вход счетчика входных импульсов производятся такие же операции с рекуррентным регистром 9 и ячейкой памяти 10 следующего младшего разряда, как описано выше. Однако переключатель этого разряда устанавливается в нулевое положение, поэтому сигнал с выхода блока 3 переноса проходит через линию задержки 6 и нулевой вход переключателя 2 и производит считывание сигнала с блока 3 переноса этого же разряда.

Таким образом осуществляется сдвиг коэффициента пересчета на один (второй) разряд.

Сигнал подготовки гоступает на вход за иси ячейки памяти 10 ;;.:адшего разряда, поступление каждого входного импульс", пригодит к срабатыванию я:ейки памяти 10 младшего разряда (правая по схеме), а черсз нес

З0

60 и к продвижению сигналов по ячейкам последовательного регистра 1 с частотой следования входных импульсов.

Ь момент поступления четвертого входного импульса сигнал поступает на выход блока 3 переноса младшего разряда и, следовательно, на выход всего счетчика.

Сигнал на выходе счетчика производит гашение импульсов во всех ячейках памяти 10 (кроме старшего разряда) и ячейках последовательного регистра 1, кроме того, он производит запись импульса подготовки в блок 3 переноса первого старшего разряда, в результате чего счетчик подготовлен к следующим полным циклам счета.

Благодаря применению блоков переноса, ячеек памяти и линий задержки, соединенных определенным способом с последовательным и рекуррентным регистрами, удается получить любой целый коэффицииет пересчета счетчика в пределах от 1 до 999 входных импульсов.

При увеличении числа разрядов счетчика на единицу в устройстве добавляется лишь ячейка памяти с линией задержки и блок переноса с линией задержки.

Длина последовательного регистра постоянна и в десятичной системе счета равна 9. Длина рекуррентного регистра выбирается из расчета числа разрядов коэффициента пересчета.

Предмет изобретения

Десятичный счетчик импульсов на ферритполупроводниковых элементах с регулируемым коэффициентом пересчета, состоящий из рекуррентного регистра сдвига с дешифратором и последовательного регистра сдвига, выход каждой ячейки которого подключен к соответствующим входам декадных переключателей коэффициента пересчета, о т л и ч а юшийся тем, что, с целью повышения надежности, выходы дешифратора подключены к продвигающим обмоткам последовательного регистра и обмоткам гашения рекуррентного регистра через ячейки памяти, выход которых соединен через собственную линию задержки с ее входом, вход повторного запуска рекуррентного регистра соединен с его обмотками гашения через линию задержки, выход переключателя каждого старшего разряда через блок переноса соединен с входами записи ячейки памяти и блока переноса последующего младшего разряда, а через линию задержки — с нулевым входом переключателя последующего младшего разряда, выходы всех блоков переноса соединены непосредственно с обмотками гашения ячеек последовательного регистра и через линию задержки — с входом записи его первой ячейки, а выход блока переноса низшего разряда подсоединен непо- . средственно к входу записи блока переноса первого старшего разряда, и через линию заде1р>кки — к нулевому входу переключателя этого разряда.

443486

Составитель В. Жуков

Техред Т. Миронова

Корректор Л. Котова

Редактор Т. Морозова

Типография, пр. Сапунова, 2

3 а к аз 689/3 Изд, № 1108 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, K-35, Раушская наб., д. 4/5