Частотно-импульсное множительно-делительное устройство

Иллюстрации

Показать всеРеферат

О П Й С А И И Е (! ) д,„вв

И ЗОБРЕТЕ К И%

Союз Соватских

Социалистимеских е еспублик (61) Зависимое от авт. свидетельства(22) Заявлено 22,05. 72(21) I786225/И-24 (Ы1) M с присоединением заявки

Гасударственный кемнтет

Сввете Мнннстрав СССР ее делам нзебретеннй н еткрытнй

9 06 f 7/52 (32) Приоритет

Опубликовано 25.09,74 Бюллетень М 35

Дата опубликования описания I5, I2, 74 (5Ç) УДК62Х.374.

00I 57 (0ЕВ.В) (72) Автор изобретения

P.В. Коровин (71) Заявитель (54) ЧАСТОТНО-4ВПГЛЬСНОЕ МНОЖИТЕБНО-ДЕЛИТИПБОЕ

УСТРОЙСТВО

Изобретение относится к вы-. числительной технике.

Известно частотйо-импульсное множительно-делительное устройство,содержащее первый и второй делители частоты, первый триггер и первую схему совпадения.

Однако в известном устройстве при преобразовании получаются значительные погрешности, вызванные тем,что время пропускания первой схемы совпадения имеет случайную составляющую, обусловленную ее управлением.

Цель изобретения-повысить точность работы устройства.

Это достигается тем что в устройство введены вто 4 триггер, вторая и третья схемы совпадения; причем выход первого делителя частоты соединен с единичным входом второго триггера, нулевой вход которого соединен с йулевым входом второго делителя частоты,вы(ходом второй схемы совпадения и

2 нулевым входом первого триггера, единичный выход второго триггера соединен с управляющим входом .. . третьей схемы совпадения,информаs ционный вход которой соединен с третьим входом всего устройства,а ее выход соединен с единичным вхо дом первого триггера,информационным входом второй схемы совпаде1о ния и счетным входом второго дели теля частоты;выход второго делителя частоты соединен с управляющим входом второй схемы совпадения.

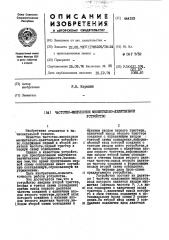

На чертеже дана блок-схема

15 предлагаемого устройства.

Устройство состоит йз делителя I частоты следования импульсов, вход которого является входом мно ,жителя (сигнала частоты F ),а вы20 ход подключен к единичному входу

; триггера 2,единичный выход которого в свою очередь подключен к по тенциальному входу схемы -;3 cosaa. дения.На второй вход схемы 3 сова Ладенйя подключен вход делителя.

444I83

Коэффициент деления частоты дели телей I m 6 выбирается из следую55 щих условий. Поскольку мгновенная частота последовательности F, меняется, необходимо чтобы был известен некоторый минимальный интервал времени Т,в течение которого среднее значение частоты

Fi должно быть не менее,чем на

2 Fa меньше среднего значения частоты Fz, 3. (сигнал частоты Fq ),а выход схемы 3 - к единичному входу триггера

4,к импульсному входу схемы 5 совпадения и через делитель 6 частоты . следования импульсов к потенциальному входу схемы 5.Выход схемы 5. совпадения подключен к нулевым входам триггеров 2 и 4 и к цепям сбро: са делителя частоты 6.Единичный выход триггера 4 подключен к потен- циальному входу схемы 7 совпадения на импульсный вход которой поступает сигнал множимого (сигнал частоты Р5 ),а выход является выходом устройства.Оба делителя частоты (I и 6) имеют один и тот .же коэффициент деления, равный й, но делитель 6,кроме того, имеет цепи сброса,при подаче импульсного сигнала на которые делитель пе реходит в исходное нулевое положение.

В исходном состоянии триггеры 2 и 4 находятся в нулевом положении,при котором схемы 3 и 7 совпадейия заперты.Оба делителя также находятся в исходном нулевом состоянии,при этом схема 5 совпадения эайерта низким потенциалом,снимаемым с последней ячейки делйтеля 6.

При подаче на все три входа устройства сигналов соответствующих частот F„ F и F,после того, как на вход делителя I поступит

М -ый импульс последовательности

F,Hà выходе делителя I получается сигнал переполнения, который поступает на единичный вход триггера 2 и перебрасывает его в единичное состояние,при котором открывается схема 3 совпадения.

Первый же сигнал, который прошел через схему З,поступает на единичный вход триггера 4 и перебрасывает его в единичное состояние,. при котором открывается схема 7 совпадения,и импульсы последовательности Fz начинают поступать на выход устройства.

Импульсы последовательности

Fz с выхода схемы 3 совпадения поступают на делитель частоты 6, где подсчитываются, и при поступлении p -ro импульса последовательности F (этот импульс появляется через р- 7 периодов последовательности Гр после момента отпирания схемы совпадения 7) на выходе делителя 6 появляется потенциал,открывающий схему совпаде-, ния 5. Следующий за этим Р+ 1

4 импульс последовательности Р проходит через схему совпадения 5,,действуя на нулевые входы триггеров 2 и 4,и переводит их в нуле5 вое состояние. При этом схемы 3 и

7 совпадения запираются, сигнал на выходе устройства времейно прекра-. щается.Одновременно с поступлениеМ на нулевые входы триггеров 2 и 4

1о сигнал с выхода схемы 5. поступает на цепи сброса делителя 6 и йереводит его в исходное н тлевое .:, состояние,при котором на выходе делителя ймеется низкий потенциал, 15 который запирает схему 5 и,все устройство (за исключением делитетеля I) находится в исходном состоянии

После прихода следующего

20 импульса с делителя I процесс повторяется.

Таким образом схема 7 совпадения открывается через каждые hf периодов последовательности Р и

ы остается открытой в течении интервала времени, равного у/р периодам последовательности Р,в течении которого на выход следуют импульсы последовательности Fq. зо Среднее значение выходной частоты в устройстве определяется из условия:

Р ц = Fg 7 х

35 где:

7-длительность интервала,в течении которого Открывается схема 7 совпадения (она равна умноженной в

40 И/д раэ длительности„периода час тоты Fg, т, е. т -> 3 ш"-число интервалов 7:7 на единицу времени, которое соответствует частоте появления импульсов на вы45 ходе делителя I m равно Стношению Fä °

Отсюда следует,что ,, Fv Й s я Я г

Составитель И ДОЛГущЕВа

Редактор Яжщщ щ Текред ЯдраыдаШОВа Корректор к. „-,.р (1. РаЬонца

Изд. И f7) тираж 6 Подписное, Заказ фД, >

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

Москва, 113035, Раушскаи наб., 4

Предприятие аПатеитэ, Москва, Г-59, Бережковская наб., 24 5

Тогда зтИиО f Cp

Однако в предлагаемом устройстве происходит задержка на .8 импульсов последовательности

F начала сигналов.Для повышения бйстродействия подключают к делителю 1 вход запуска так,чтобы сигнал на атом входе переводил делитель-в состояние, соответствующее насчету числа импульсов,на единицу мейьшего,чем выбранный коэффициент делейия.В атом случае первый же импульс последовательности F,ñëåäóþùèé за сигналом запуска,йоступает на выход делите

m и начинает работу устройства.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

Частотно-импульсное множительно-делительное устройство, содержащее первый и второй делители частоты, первый триггер и первую схему совпадения, причем счетный вход первого делителя частоты соединен с первым входом устройства;единичный выход перво.8 го триггера соединен с управляющим входом первой схемы совпадения,информационный вход которой соединен со вторым входом устрой- .

5 ства,а ее выход соединен с выходом устройства, отличающееся тем, что,с целью повышения точности работы,в него введены второй триггер,вторая и третья схемы совпа1о денйя;причем выход первого делителя частоты соединен с единичным входом второго триггера, нулевой выход которого соединен с нулевым входом второго делителя частоты, gg выходом второй схемы совпадения и нулевым входом первого триггера, единичный выход второго триггера соединен с управляющим входом третьей схемы совпадения,ин4ормаао ционный вход которой соединен с ,третьим входом устройства,а ее .-выход соединен с единичным входом первого триггера, информационным, входом второй схемы совпадения и

2; счетным входом второго делителя частоты;выход второго делителя частоты соединен с управляющим .входом второй схемы совпадения.