Формирователь адреса сканирующего устройства

Иллюстрации

Показать всеРеферат

Я

1.

l !!

Р

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ (1)) .<44188

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Г

Ф1) Зависимое от авт. свид-ва

- i! (22) Заявлено 11.08.72 (21) 1818220/18 24 (51) М. Кл. Q 06 f 15/20 с присоединением заявки №вЂ” (32)Приоритет

Государственный комитет

Совета Министров СССР па делам иэаоретеннй и открытий

Опубликовано 25.09.74,Бюллетень №35 (53) УДК 681.325. (088.8) Дата опубликования описания 1806.75 (72) Автор.. изобретения

И. М. Соколов (71) Заявитель (54) ФОРМИРОВАТЕЛЬ АДРЕСА СКАНИРУЮТ!ЕГО

УСТРОЙСТВА

Изобретение относится к вычислительной технике, в частности к устройствам управления, и может быть использовано для уп» равления сканированием луча фазированной антенной решетки.

Известен формирователь адреса сканирующего устройства, содержащий сумматор, устройство памяти сектора сканирования, связанное с устройством памяти исходных данных, датчик коррекции адреса, связанный с преобразователем, устройство управления и регистр адреса.

Однако при увеличении числа каналов формирования адреса в устройстве пропорционально возрастают затраты оборудования.

llew изобретения — расширение функциональных возможностей формирователя. Для этого предлагаемый формирователь содержит устройство памяти сектора сканирования, устройство памяти исходных данных, преобразователь, регистр адреса, первый и второй коммутаторы, причем входы регист ров адреса подключены к выходам сумматора, один вход которого связан с выхо-дом датчика коррекции через первый коммутатор и преобразователи, другой вход сумматора соединен через первый коммутатор с выходами устройств памяти сектора сканирования, входы которых соединены с выходами устройств памяти исходных данных, преобГазователи, устройства памя-. ти сектора сканирования и регистры адреса подключены к устройству управления че 0 рез второй коммутатор, который как и первый коммутатор соединен с переключате> лем каналов, выполненным, например, на триггере, подключенном к генератору устройства управления.

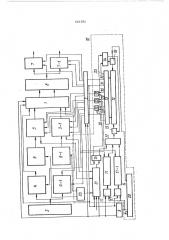

15 На чертеже представлена блок-схема формирователя адреса сканирующего устройства.

Формирователь содержит коммутаторы

1, 2, датчик коррекции адреса 3, преобраап,зователи 4 и 4-1, устройства памяти сектора сканирования 5 и 5-1, устройства памяти исходных данных 6 и 6-1, регист ры адреса 7 и 7-1 ° сумматор S, триггер

9, устройство управления 10 в состав кора торого входят устройства l l и 1 1-1 фор-.

444188 мирования частоты смены адреса, счетчик

12, дешифратор 13, триггеры 14 и 15, схемы "И" — ключи 16-19, генератор 20, ф<эрлшрователь 21 общего сброса, схемы

"ИЛИ" 22, переключатель режима 23 и схемы "И" 24 и 25.

Формирователь адреса сканирующего устройства работает следующим образом.

После установки режима работы переключателем 23 (или после прихода внешнего сигнала сброса) на выходе формирователя 21 общего сброса возникает импульс, обеспечивающий срабатывание триггера 15, что приводит к сбросу счетчика

12 и к появлению сигнала на нулевой шине 26 дешифратора 13, обеспечиванэщего срабатывание триггера 14, Триггер 14 подключает вход счетчика 12 к выходу генератора 20, выдающего импульсы с частотой f и отключает схему И" 19. (.;игнян, снимаемый со второго выхода генератора 20 (f „ f ), подается ня

2 1 счет пэй вход триггера 9, ко орый обеснечивяет подключение верхнего или нижнего канала формирователя адресd сканирукэшего устройства (предположим, чго и данный момент будег llojlEJIII» Iåí верхний канал). При поступлении нмпуньссаз Н» вход с ч от чик а 1 2 на выходе де шифра тора 1 3 поочередно возникают илглуцьсъэ Hcl шинах

27-33.

Сиэ»ган, снимаемый с шины 27, обесэнс.— чивяет стирание редыдушей пни>рмании преобразователя 4 и нодкнк чс:нисз f. го к датчику коррекции яд!эсзся 3 и с»эрнс.ивясэ устройство формиронания гяс l оты смены адреса 1 1.

Сигнал, снилсасзлэый с шины 28, обес:цечиваег сброс ус»ройства памяти секгоря сканирования 5. (.,HI нян, I-.íèl làåìülé с шинаl 29, обесцечиваег подключение рьч исг!эсэвсн 0 входа устройства памяти сел го!за с кянирования 5 = к выходу устройства пяматн исходных

Ф данных 6. Сигнал, снимаемый с шины 30, не проходит ня счетный вход yc ö)ÎÉcòèè памяти сектора сканирования 5, так как триггер 15 откнючает логическую схему

И" 18.

Сигнал, снимаемый с шины 31, обеспечивает сброс реги<.тра адреса 7 и .триггеB 1,5э (.игнал, снимаемый с шины 32, обеспечивает подключение регистра адреса 7 к выходу сумматора 8. (. .игнал, снимаемый с шины 33, обеспечцвает срабатывание трип ера 14, отклк - .

10

25 чающего ключ 16 и подключающего ключи

17 и 19.

После прихода второго импульса с частотой f триггер 9 обеспечивает под» ключение нижнего канала при наличии сигнала от переключателя режимов или внешнего импульса общего сброса. При этом нижний канал работает аналогично верхнему, но в формировании адреса принимает участие регистр адреса 7-1, сумматор 8, коммутатор 1, устройство памяти сектора сканирования 5-1, устройство памяти исходных данных 6-1, преобразователь 4-1, ратчик коррекции адреса 3, устройство

11-1 формирования частоты смены адреса и устройство управления 10, После прихода третьего импульса с частотой, триггер 9 вновь подключает верхний канал, но устройство управления н .. работает, так кяк, например, в устройстве формирования частоты смены адреса установили задержку, равную двум, и поэтому сброса счетчика 1 2 не происходит.

После прихода четвертого импульса с чистотой f, триггер 9 вновь подключает

55 нижний канал и если задержка в устройсгве формирования частоты смены адреса отсутствуег, то формирование адреса идеэ по аналогии, кяк было при втором импульсе с частотой f,, только сброс и pevucrpo2 вый вход устройства памяти секто1эа сканн" ровяния 5-1 будет отключен, его счетный вход подключен, а значит при каждом обращении к устройству управлении .10 буде! происходигь изменение адреса.

После прихода пятого импульса с час готой f триггер О,рцовь подк>гючает . I верхний канал. Так как зядержка в устрой<л»зе формирования частоты смены адреса

1 1 Кратна двум, то при питом импульсе сигнал проходит в цепь сброса счетчика

12, я значит происходит формирование нового адреса, аиалсп ично, как при четвертом импульсе в нижнем канале, и т. д, По мере заполнения того или иного канала с соответствующего устройства памяти сек»ора сканирования 5 или 5-1 поступает сигнал в формирователь 21 общего сброса, после чего соответствующий канал устанавливается в исходное состояние; зятем цикл работы повторяется в соответствующем канале.

Предмет изобретения I

g 1с Форлсирователь адреса сканирующего устройства, содержащий сумматор, усгройство памяти сектора сканирования, связан444188 ное с устройством памяти исходных данных, датчик коррекции адреса, связанный с преобразователем, устройство управления и регистр адреса, отличающийся тем, что, с целью расширения функциональ- 5 ных возможностей формирователя, он содержит первый и второй коммутаторы, дополнительное устройство памяти исходных данных, соединенное с входом дополнительного устройства памяти сектора ска- )9 нирования, дополнительный преобразователь, соединенный с датчиком коррекции адреса, дополнительный регистр адреса, причем входы регистров адреса подключены к выходам сумматора, один вход которого свя- 15

6 зан с выходом датчика коррекции адреса через первый коммутатор и преобразователи, другой вход сумматора соединен через первый коммутатор с выходами устройств памяти сектора сканирования, входы которых соединены с выходами устройств памяти исходных данных, преобразователи, устройства памяти сектора сканирования и регистры адреса подключены к устройству управления через второй коммутатор, который как и первый коммутатор, соединен с переключателем каналов, выполненным, например, на триггере, подключенном к генератору устройства управления.