Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

(i <) 44424О

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 31.10.72 (21) 1842135/18-24 к с присоединением заявки Ае

Государственный комитет (32) Пр р

Совета Министров СССР

Опубликовано 25.09.74. Бюллетень Хе 35 (51) М. Кл. G 11c 11/00 (53) УДК 681.327.6 (088.8) по делам изобретений и открытий

Дата опубликования описания 12.11.75 (72) Авторы изобретения

В. С. Голубев и В. И. Агафонов (71) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Известно буферное запоминающее устройство, содержащее накопители, входы которых подключены к дешифратору адреса, а выходы — к одним входам схем выделения сигналов, коммутатор, выходы которого подсоединены к входам дешифратора адреса, а первые входы — к одному из датчиков адреса, делители частоты, схемы формирования контрольных символов, ключевые схемы, входы которых соединены с шинами обращения, схемы выделения сигналов.

Цель изобретения — увеличение эффективности емкости устройства.

Предлагаемое буферное запоминающее устройство отличается от известного тем, что в него введены инверторы по количеству выходов датчика адреса, входы которых подключены к выходам другого датчика адреса, а выходы — ко вторым входам коммутатора, схемы

«ИЛИ», одни входы которых подсоединены соответственно к выходам ключевых схем и к входным шинам устройства, другие входы— к выходам делителей частоты и схем формирования контрольных символов, а выходы — к входам датчиков адреса и накопителей, выходы делителей частоты подключены соответственно к входам схем формирования контрольных символов и к входам схем выделения сигналов, выходы которых подсоединены к выходным шинам устройства.

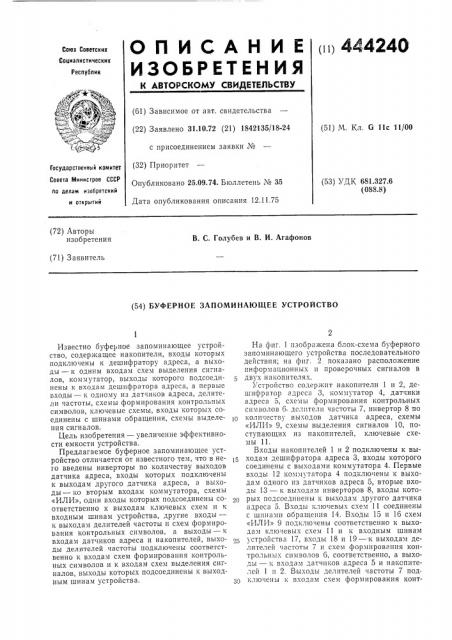

На фиг. 1 изображена блок-схема буферного запоминающего устройства последовательного действия; на фиг. 2 показано расположение информационных и проверочных сигналов в двух накопителях.

Устройство содержит накопители 1 и 2, дешифратор адреса 3, коммутатор 4, датчики адреса 5, схемы формирования контрольных символов 6. делители частоты 7, инвертор 8 по и количеству выходов датчика адреса, схемы

«ИЛИ» 9, схемы выделения сигналов 10, поступающих из накопителей, ключевые схемы 11.

Входы накопителей 1 и 2 подключены к выходам дешифратора адреса 3, входы которого соединены с выходами коммутатора 4. Первые входы 12 коммутатора 4 подключены к выходам одного из датчиков адреса 5, вторые входы 13 — к выходам пнверторов 8, входы которых подсоединены к выходам другого датчика адреса 5. Входы ключевых схезт 11 соединены с шинами обращения 14. Входы 15 и 16 схем

«ИЛИ» 9 подклточены соответственно к выходам ключевых схем 11 и к входным шинам устройства !7, входы 18 и 19 — K выходам делителей частоты 7 и схем формирования контрольных символов 6, соответственно, а выходы — к входам датчиков адреса 5 и накопите",åé 1 и 2. Выходы делителей частоты 7 подключены к входам схем формирования конт444240

10 !

Зо

-.0

55 рольных символов 6 и к входам 20 схем выделения сигналов 10, выходы которых подсоединены к выходным шинам 21 устройства. Другие входы схем выделения сигналов связаны с выходами накопителей 1 и 2 и шинами îáращения 14.

Устройство работает следующим образом.

При записи информации в накопитель сигналы обращения с частотой F> поступают на шину 14 и через схему 11 и 9 проходят на вход датчика адреса 5, который с каждым сигналом, поступающим на его вход, формирует код адреса. Код адреса через коммутатор 4 передается в дешифратор 5, который обеспечивает выбор ячейки памяти в накопителе 1.

Информация содержащаяся в ячейках памяти того же адреса накопителя 2 перезаписывается по цепи регенерации (на чертеже не показана).

По выбранному адресу осуществляется запись информационных символов в накопитель 1 и контрольных символов в накопитель 2 (один раз за и тактов обращения к первому накопителю, где n — коли-.ество информационных символов, преходящееся на один контрольный). Каждый такт обращения по частоте

F(, сопровождается тактом обращения по частоте F>, который не поступает на вход датчика адреса 5 накопителя 2, а поступает через делитель 7 на вход датчика адреса 5 накопителя 1 и производит в нем схему кода адреса, по которому запись информации в накопитель 1 не производится.

Таким образом, в накопителе 1 остаются незаполненные ячейки через каждые и заполненных ячеек.

Обращение к накопителю 2 осуществляется аналогично по частоте F . При этом предварительно меняется положение ключевых схем 11 и контактов коммутатора 4 на противоположное. Отличие заключается в том, что за счет включения инверторов 8 к выходам датчика адреса 5 накопителя 2 выборка ячеек памяти в накопителе идет в последовательности обратной, чем в первом случае.

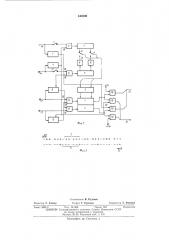

При работе устройства информация в накопителях 1 и 2 располагается, как показано на фиг. 2. На ней знаком « — » обозначено расположение информационных и контрольных символов в одном накопителе, а знаком «+»вЂ” расположение информационных и контрольных символов в другом накопителе. Стрелки 22 указывают последовательность выборки ячеек памяти при вводе и выводе информационных и контрольных символов из соответствующих накопителей.

Для того, чтобы расположение информационных и контрольных символов и накопителях осуществлялось в соответствии с фиг. 2, т. е. не происходило наложения информационных символов одного накопителя на контрольные символы информации, хранящейся в другом накопителе, должно соблюдаться условие установки начальпых адресов в датчиках кода адреса. Если емкость каждого из накопителей кратна величине (и+1), то за начальный адрес в каждом из датчиков кода адреса следует принять код, соответствующий второй ячейке памяти в накопителе 1. Очевидно, что этот код с учетом инверсии оудет соответствовать предпоследней ячейке памяти в накопителе 2.

Считывание информационных и контрольных символов из накопителей осуществляется по соответствующим сигналам обращения в порядке, аналогичном режиму записи.

При этом в зависимости от обращения на схему выделения сигналов, поступающих из накопителя, подаются стробирующие импульсы, «привязанные» к сигналам обращения. Информация, считанная из накопителя, к которо»у обращение не производится, перезаписывается по цепи регенерации (па чертеже не показана). При этом не перезаписывается содержимое ячеек памяти, соответствующих каждому и сигналу обращения к выбранному накопителю.

Предмет изобретения

Буферное запоминающее устройство, содержащее накопители, входы которых подключены к дешифратору адреса, а выходы — к одним входам схем выделения сигналов, коммутатор, выходы которого подсоединены к входам дешифратора адреса, а первые входы— к одному из датчиков адреса, делители частоты, схемы формирования контрольных символов, ключевые схемы, входы которых соединены с шинами обращения, схемы выделения сигналов, отл н ч а ю щеес я тем, что, с целью увеличения эффективной емкости устройства, оно содержит инверторы по количеству выходов датчика адреса, входы которых подключены к выходам другого датчика адреса, а выходы — к вторым входам коммутатора, схемы «ИЛИ», одни входы которых подсоединены соответственно к выходам ключевых схем и к входным шинам устройства, другие входы — к выходам делителей частоты и схем формирования контрольных символов, а выходы — к входам датчиков адреса и накопителей, выходы делителей частоты подключены соответственно к входам схем формирования контрольных символов и к входам схем выделения сигналов, выходы которых подсоединены к выходным шинам устройства.

444240 к 70 г — ++ +1+ ++ ++ ++ +4+ — (+1 +++ гг

Составитель В. Рудаков

Текред Т. Курилко

Редактор E. Гончар

Корректор T. Фисенко

Типография, пр. Сапунова, 2

Заказ 2691)2 Изд. М 869 Тираж 593 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5