Ячейка памяти

Иллюстрации

Показать всеРеферат

111 444244

О П И С А Н И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз. Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 1 2.04.73 (21) 1907687/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 25.09.74. Бюллетень № 35

Дата опубликования описания 25.04.75 (51) М. Кл. G llс 11/40

Государственный комитет

Совета Министров СССР (53) УДК 681.327.066 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. В. Прушинский, А. Г. Филиппов, Н. Л. Пуппинь, А. П. Удовик, А. С. Савлук и И. А. Аракчеева (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение касается вычислительной техники и предназначено для использования в качестве запоминающего элемента в оперативных запоминающих устройствах цифровых вычислительных систем.

Известны ячейки памяти, содержащие два двухэмиттерных транзистора и — р — и типа, коллектор первого из которых соединен с базой второго, коллектор второго соединен с базой первого, первые эмиттеры двухэмиттерных транзисторов подключены с соответствующим разрядным шинам, а вторые— объединены. В ячейках этого типа в момент записи и считывания информации изменяется величина коллекторной нагрузки с целью увеличения быстродействия.

Такие ячейки памяти характеризуются сложностью схемы, обусловленной наличием большого количества пассивных компонентов, что снижает надежность схемы, а также значительной мощностью, потребляемой в режиме хранения информации и невысоким быстродействием вследствие малого диапазона изменения тока в ячейке при переходе от режима хранения информации в режим записи— считывания информации.

Цель изобретения — повышение надежности, снижение потребляемой мощности в режиме хранения информации и увеличение быстродействия ячейки.

Зто достигается введением двух нагрузочных и двух переключающих транзисторов р — и — р типа, причем коллекторы первого двухэмиттерного, первого нагрузочного и второго переключающего транзисторов подключены к базе первого переключающего транзистора, коллекторы второго двухэмиттерного, второго нагрузочного и первого переключающего транзисторов подключены к базе второго переключающего транзистора, эмиттеры переключающих транзисторов и вторые эмиттеры двухэмиттерных транзисторов подключены к числовоп шине, эмиттеры нагрузочных транзисторов подключены к шине питания, а базы нагрузочных транзисторов подключены к шине смещения.

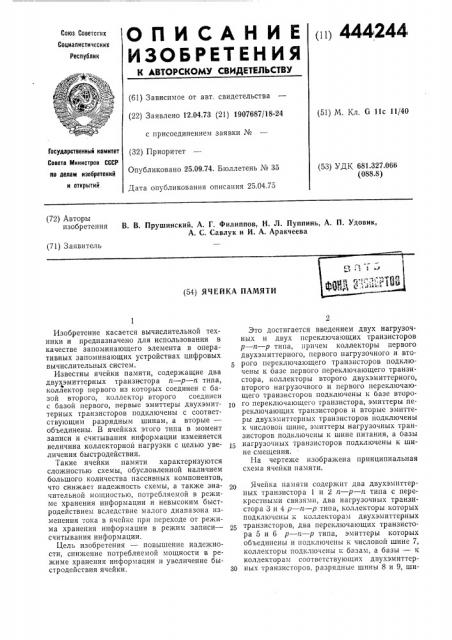

На чертеже изображена принципиальная схема ячейки памяти.

Ячейка памяти содержит два двухэмиттерных транзистора 1 и 2 и — р — и типа с перекрестными связями, два нагрузочных транзистора 3 и 4 р — и — р типа, коллекторы которых подключены и коллекторам двухэмиттерных транзисторов, два переключающих транзистора 5 и G р — n — р типа, эмиттеры которых объединены и подключены к числовой шине 7, коллекторы подключены и базам, а базы — и коллекторам соответствующих двухэмиттерЗО ных транзисторов, разрядные шины 8 и 9, ши444244 ну питания 10, шину смещения 11, усилители

12 и 13 записи — считывания.

Ячейка памяти работает в трех режимах: в режиме хранения информации, в режиме считывания информации и в режиме записи информации.

В режиме хранения информации один из двухэмиттерных транзисторов 1 или 2 насыщен, а на числовой шине 7 установлен низкий уровень потенциала. Нагрузочные транзисто- 10 ры р — и — р типа 3 и 4 являются источниками тока и поддерживают ячейку в одном из двух устойчивых состояний в режиме хранения информации. Переключающие транзисторы р — и — р типа 5 и 6 в этом режиме закрыты и 15 не влияют на работу схемы.

Пусть перед считыванием информации двухэмиттерный транзистор 1 был насыщен. При подаче положительного импульса считывания — записи на числовую шину 7 открывает- 20 ся транзистор 5, так как база его оказывается подключенной к насыщенному транзистору 1. Эмиттерный ток насыщенного транзистора 1 резко увеличивается, что обеспечивает резкое повышение напряжения на разрядной 25 шине 8 и быстрое включение усилителя считывания 12. При этом за счет коллекторного тока транзистора 5 обеспечивается увеличение тока базы транзистора 1, необходимое для поддержания его в насыщенном состоянии, 30 так как коллектор ного тока нагруз очного транзистора 4 в момент считывания информации для этого недостаточно. Транзисторы второго плеча триггера 2 и 6 закрыты из-за недостаточного напряжения на переходах база в 35 эмиттер. После считывания информации напряжение на числовой шине 7 понижается и ячейка возвращается в режим хранения информации, не меняя своего состояния.

В режиме записи информации на одной из 40 разрядных шин, например на шине 9, с помощью усилителя 13 записи — считывания устанавливается низкий уровень потенциала. Тогда, после подачи импульса на числовую шину

7 ток течет через переход эмиттер — база пе- 45 реключающего транзистора 5 в базу двухэмиттерного транзистора 2, к эмиттеру которого приложен низкий уровень потенциала.

Двухэмиттерный транзистор 2 открывается и током коллектора этого транзистора закры- 50 вается транзистор I, а также открывается переключающий транзистор 6. Током коллектора переключающего транзистора 6 закрывается переключающий транзистор 5 и поддерживается в насыщении двухэмиттерный транзистор 2. Ячейка переключилась в другое состояние. После записи информации напряжение на числовой шине 7 понижается и ячейка возвращается в режим хранения информации, изменив свое состояние.

Ячейка памяти проста по конструкции, так как транзисторы 1 и 5, 2 и 6 попарно выполняются в одной п-области, а нагрузочные транзисторы 3 и 4 выполнены в общей и-области для всей матрицы памяти. Так как мощность, потребляемая ячейкой в режиме хранения информации, на несколько порядков ниже мощности, потребляемой в режимах считывания †запи, а частота обращения к данному кристаллу оперативного запоминающего устройства невысока, средняя мощность, потребляемая интегральным оперативным запоминающим устройством, изготовленным на основе предлагаемой транзисторной ячейки памяти, будет значительно меньше, чем у существующих образцов быстродействующих интегральных запоминающих устройств на биполярных транзисторах.

Предмет изобретения

Ячейка памяти, содер>кащая два двухэмиттерных транзистора и — р — и типа, коллектор первого из которых соединен с базой второго, коллектор второго соединен с базой первого, первые эмиттеры двухэмиттерных транзисторов подключены к соответствующим разрядным шинам, а вторые объединены, о т л и ч аю щ а я с я тем, что, с целью повышения наде>кности, снижения потребляемой мощности в режиме хранения информации и увеличения быстродействия, опа содержит два нагрузочных и два переключающих транзистора р — и — р типа, причем коллекторы первого двухэмиттерного, первого нагрузочного и второго переключающего транзисторов подключены к базе первого переключающего транзистора, коллекторы второго двухэмиттерного, второго нагрузочного и первого переключающего транзисторов подключены к базе второго переключающего транзистора, эмиттеры переключающих транзисторов и вторые эмиттеры двухэмиттерных транзисторов подключены к числовой шине, эмиттеры нагрузочных транзисторов подключены к шине питания, а базы нагрузочных транзисторов подключены к шине смещения.

444244

Составитель В. Голубкова

Редактор А. Морозова Техред В. Рыбакова Корректоры; В. Петрова и О. Данишева

Заказ 973/7 Изд. Мв 476 Тираж 591 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2