Ячейка памяти

Иллюстрации

Показать всеРеферат

ОП ИСА

ИЗОБРЕТЕНИЯ

ЙИЕ

1п1 444245

Союз Советских

Соцналнстнческик

Республнк

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 07.02.73 (21) 1880840/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 25.09.74. Бюллетень ¹ 35

Дата опубликования описания 28.04.75 (51) М. Кл. G llс 11/40

Государственный комитет

Совета Министров СССР по делам изобретений н открытий (53) УДК 681.327.006 (088.8) (72) Авторы изобретения

В. В. Прушинский, А. Г. Филиппов, А. П. Удовик, А. С. Савлук и И. А. Пракчеева (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Ячейка памяти касается вычислительной техники и предназначена для использования в качестве элементарного запоминающего элемента в интегральных полупроводниковых матрицах памяти оперативных запоминающих устройств цифровых вычислительных машин.

Известны ячейки памяти, содержащие два многоэмиттерных п — р — п транзистора, эмиттер первого из которых соединен с базой второго,а эмиттер второго †базой первого, и два токозадающих р — п — р транзистора.

Такие ячейки характеризуются невысоким быстродействием и значительной потребляемой мощностью из-за потерь в нагрузочных р — п — р транзисторах с горизонтальной инжекцией.

Цель предлагаемого изобретения — увеличение быстродействия и уменьшение потребляемой мощности.

Это достигается введением в каждый многоэмиттерный транзистор п — р — п типа по дополнительному эмиттеру, которые через резитор подключены к шине источника питания, а коллекторы многоэмиттерных транзисторов п — р — п типа подключены к базам транзисторов р — п — р типа, соединенным между собой.

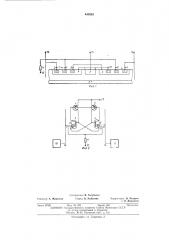

На фиг. 1 представлена ячейка, выполненная методом интегральной технологии в общей и-области; на фиг. 2 — принципиальная схема ячейки.

Ячейка содержит инжектирующие транзисторы 1 и 2 р — п — р типа, управляющие многоэмиттерные транзисторы 3 и 4 п — р — п типа с разрядными эмиттерами 5 и 6 считыва5 ния записи, эмиттерами 7 и 8 хранения и эмиттерами 9 и 10 обратной связи, а также резистор 11, связывающий эмиттеры хранения с шиной 12 питания. Эмиттеры инжектирующих транзисторов подсоединены к шине 13 пита10 ния. Разрядные шины 14 и 15 соединяют разрядные эмиттеры с усилителями 16 и 17 считывания записи.

Ячейка работает в трех режимах: в режиме хранения информации, в режиме считывания

15 информации, в режиме записи информации.

Пусть в режиме хранения информации транзистор 4 насыщен. Тогда ток, протекающий от источника по шине 13 питания через транзистор 2, попадает в базу транзистора 4 и под20 держивает его в насыщенном состоянии. Ток, протекающий через транзистор 1, направляется к эмиттеру 10 обратной связи, поэтому транзистор 3 остается закрытым.

Транзисторы 1 и 2 постоянно поддержива25 ются в открытом состоянии коллекторным током одного из открытых транзисторов 3 или

4. Ток насыщенного транзистора 4 через эмиттер хранения течет в резистор 11. который является в режиме хранения информации токоЗо задающим. Этот резистор может выполняться

- 444245

1О

25 зо как для каждой ячейки в отдельности, так и общим для ряда ячеек в зависимости от степени развития технологии.

В момент считывания информации напряжение на шине 13 питания повышается. Соответственно повышается напряжение на резисторе 11 и на разрядном эмиттере б насыщенного транзистора 4, который подключен к разрядной шине 15. Часть тока от источника питания, протекая в разрядную шину 15 через насыщенные транзисторы 1, 2 и 4, включает усилитель считывания — записи 17. На выходе усилителя 17 формируется импульс, соответствующий записанной информации.

После считывания информации напряжение на шине 13 питания уменьшается и ячейка переходит вновь в режим хранения информации, не меняя своего состояния.

Для записи информации на одной из разрядных шин, к примеру на шине 14, с помощью усилителя 16 считывания — записи устанавливается низкий уровень потенциала. Тогда, после повышения напряжения на шине 13 питания ток, протекающий через коллектор насыщенного транзистора 1, переключается в базу транзистора 3, так как на разрядный эмиттер 5 этого транзистора подается низкий уровень потенциала. Транзистор 3 насыщается и током эмиттера обратной связи 9 закрывает транзистор 4. Схема переключалась в другое состояние. После записи информации напряжение на шине питания уменьшается, ток насыщенного транзистора 3 переключается в эмиттер 7 хранения и в резистор 1f,, а ячейка переходит в режим хранения информации уже в новом состоянии.

Ток в режиме хранения информации может быть на несколько порядков меньше тока, включающего усилитель считывания информации и тока, переключающего ячейку в другое состояние в момент записи информации, чем обеспечивается малая потребляемая мощность. В то же время в схеме предусмотрен высокий уровень токов в режимах записи и считывания информации, что обеспечивает высокое быстродействие ячейки памяти.

Ячейка памяти изготавливается обычными методами интегральной технологии, применяемыми при производстве схем на биполярных транзисторах.

П р едм ет изобретения

Ячейка памяти, содержащая два многоэмиттерных и — р — и транзистора, эмиттер первого из которых соединен с базой второго, а эмиттер второго — с базой первого и два токозадающих p — n — р транзистора, о т л и ч а ю щ а яс я тем, что, с целью увеличения быстродействия и уменьшения потребляемой мощности, каждый многоэмиттерный транзистор и — р — и типа содержит по дополнительному эмиттеру„ которые через резистор подключены к шине источника питания, а коллекторы многоэмиттерных транзисторов п — р — и типа подключены к базам транзисторов р — п — р типа, соединенным между собой.

444245 моиг 1

Фиг. 2

Редактор А. Морозова

Заказ 973/8 Изд. М 476 Тираж 591 Подппсно

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4,, 5

Типография, пр. Сапунова, 2

Яб

Составитель В. Голубкова

Техред В. Рыбакова

Корректоры: В. Петрова и О. Данишева