-разрядный сдвигающий регистр

Иллюстрации

Показать всеРеферат

сш 444249

ОЛИ САН И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз. Советских

Сониалистическнх

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 12.04.73 (21) 1907688/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 25.09.74. Бюллетень ¹ 35

Дата опубликования описания 25.04.75 (51) М. Кл, G 11с 19/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.327.066 (088.8) (72) Авторы изобретения А. Г. филиппов, В. В. Прушинскии, В. М. Белопольский, А. П. Удовик„

В. А. Иванов, А. С. Савлук и В. М. Мамута (71) Заявитель (54) Л -РАЗРЯДНЪ|Й СДВИГАЮЩИЙ РЕГИСТР

Изобретение относится к области вычислительной техники и может использоваться в цифровых вычислительных устройствах.

Известны сдвигающие регистры, каждый разряд которых состоит из двух полутактовых триггерных ячеек, каждая из которых включает два двухэмиттерных транзистора, причем коллектор первого подключен к базе второго и к первому резистору, а коллектор второго— к базе первого и ко второму резистору.

Однако известный сдвигающий регистр имеет невысокое быстродействие, так как следующая ячейка переключается частью тока, текущего через одно из коллекторных сопротивлений. Кроме того, такие ячейки критичны к параметрам активных компонентов схемы, что снижает надежность регистра.

Цель изобретения — повысить надежность и увеличить быстродействие устройства.

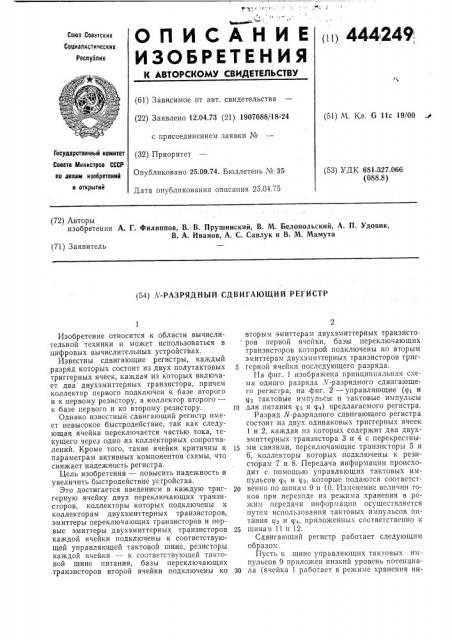

Это достигается введением в каждую триггерную ячейку двух переключающих транзисторов, коллекторы которых подключены к коллекторам двухэмиттерных транзисторов, эмиттеры переключающих транзисторов и первые эмиттеры двухэмиттерных транзисторов каждой ячейки подключены к соответствующей управляющей тактовой шине, резисторы каждой ячейки — к соответствующей тактовой шине питания, базы переключающих транзисторов второй ячейки подключены ко вторым эмиттерам двухэмиттерных транзисторов первой ячейки, базы переключающих транзисторов которой подключены ко вторым эмиттерам двухэмиттерных транзисторов триг5 герной ячейки последующего разряда.

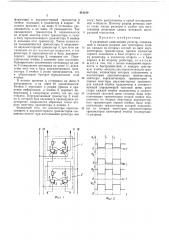

На фиг, 1 изображена принципиальная схема одного разряда Л -разрядного сдвигающего регистра; на .фиг. 2 — управляющие (qi и ср2 тактовые импульсы и тактовые импульсы

10 для питания Va и ср4) предлагаемого регистра.

Разряд Ж-разрядного сдвигающего регистра состоит из двух одинаковых триггерных ячеек

1 и 2, каждая из которых содержит два двухэмиттерных транзистора 3 и 4 с перекрестны15 ми связями,. переключающие транзисторы 5 и

6, коллекторы которых подключены к резисторам 7 и 8. Передача информации происходит с помощью управляющих тактовых импульсов срс и срз, которые подаются соответст20 венно по шинам 9 и 10. Изменение величин токов при переходе из режима хранения в режим передачи информации осуществляется путем использования тактовых импульсов питания срз и ср4, приложенных соответственно к

25 шинам 11 и 12.

Сдвигающий регистр работает следующим образом.

Пусть к шине управляющих тактовых импульсов 9 приложен низкий уровень потенциа30 ла (ячейка 1 работает в режиме хранения ин444249

Ри8 ) Фиг 2 формации) и двухэмиттерный транзистор 3 ячейки насыщен, а транзистор 4 закрыт. В момент времени t на шине 9 потенциал увеличивается, а на шине 10 уменьшается, Ток насыщенного транзистора 3 переключается во второй эмиттер этого транзистора и течет в базу переключающего транзистора 5 ячейки

2, насыщая этот транзистор. Током коллектора насыщающегося транзистора 5 закрывается двухэмиттерный транзистор 4, при этом напряжение на его коллекторе возрастает, и ток резистора 8 переключается в базу двухэмиттерного транзистора 3, открывая его. Переключаемая ячейка 2 изменяет свое состояние.

Одновременно увеличением потенциала на шине 9 повышается потенциал на шине 11, вследствие чего ток в базу переключающего транзистора 5 ячейки 2 резко увеличивается, что и обеспечивает быстрое переключение этой ячейки..

В момент времени tz потенциал на шине 9 уменьшается, а на шине 10 увеличивается.

Ячейка 1 переходит в режйм приема и хранения информации, а ячейка 2 передает информацию в следующую ячейку так же, как описано. Переключающий транзистор 5 ячейки 2, который был насыщен в предыдущем полупериоде, закрывается обратным током второго эмиттера транзистора 3 ячейки 1.

Вследствие того, что коллекторы переключающего и двухэмиттерного транзисторов соединены вместе, при изготовлении регистра они могут быть расположены в одной изолированной и-области. Поэтому разряд регистра имеет очень малые размеры и удобен при изготовлении регистров сдвига методами интег5 ральной технологии.

Предмет изобретения

N-разрядный сдвигающий регистр, содержащий в каждом разряде две триггерные ячей10 ки, каждая из которых состоит из двух двухэмиттерных транзисторов, причем коллектор первого подключен к базе второго и к первому резистору, а коллектор второго — к базе первого и ко второму резистору, о т л и ч а ю15 шийся тем, что, с целью повышения надежности и быстродействия, в каждую триггерную ячейку введены два переключающих транзистора, коллекторы которых подключены к коллекторам двухэмиттерных транзисторов, 20 эмиттеры переключающих транзисторов и первые эмиттеры двухэмиттерных транзисторов каждой ячейки подключены к соответствующей управляющей тактовой шине, резисторы каждой ячейки подключены к соответ25 ствующей тактовой шине питания, базы переключающих транзисторов второй ячейки подключены ко вторым эмиттерам двухэмиттерных транзисторов первой ячейки, базы переключающих транзисторов которой подключе30 ны ко вторым эмиттерам двухэмиттерных транзисторов триггерной ячейки последующего разряда.