Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и) 444250

Cess Ьввтвва

Социалистических

Реслублик (61) Зависимое от авт. свидетельства (22) Заявлено 19.03.73 (21) 1896539/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 25.09.74. Бюллетень № 35

Дата опубликования описания 07.04.75 (51) М. Кл. G llc 29/00

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.321.6 (088.8) (72) Авторы изобретения К. Г. Самофалов, В. И. Корнейчук, А. В. Городний и А. И. Небукин (71) Заявитель Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С АВТОНОМНЫМ КОНТРОЛЕМ

Изобретение относится к запоминающим устройствам, Известно запоминающее устройство с автономным контролем, содержащее накопитель, подключенный к одному блоку схем

«ИЛИ» и регистру кодового слова, блоки кодирования и декодирования, подсоединенные к регистру силы корректирующего кода, схеме сравнения, схеме определения кратности отказа, блоки схем «И», подключенные к регистру кодового слова, тритгеру, другому блоку схем «ИЛИ» и блоку управления.

Однако в известном устройстве повышение иоправляю|цей способности блоков кодирова ния и декодирования по мере накопления отказов в ячейках накопителя связано с большими приращениями информационной избы-. точности и с высокой общей инфромационной из|быточносгью, используемой блоками кодирования и декодирования, что значительно снижает эффективную емкость устройства.

Описываемое устройство отличается от извест ного тем, что оно содержит дополнительные схемы «И», дополнительный триггер и регистр мощности корректирующего кода, один вход первой дополнительной схемы «И» подключен к выходу схемы сравнения, другой — к блоку управления, а выход — к одному из входов дополнительного триггера, другой вход которог0 подсоединен к блоку управления, а выход — к одному из входов второй дополнительной схемы «И», другой вход которой подключен к выходу схемы сравнения, а выход — ко входу регистра мощности корректирующего кода, выход которого соединен со входами блоков кодирования и декодирования.

Это позволяет повысить эффективную емкость устройства.

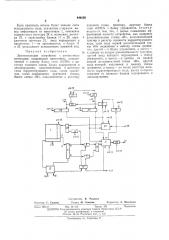

10 На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит накопитель 1, имеющий информационный вход 2, кодовый выход

3 накопителя 1 соединен со входом 4 регист15 ра 5 кодового слова. Прямой выход 6 регистра 5 через блок схем «И» 7, а инверсный выход 8 через блок схем «И» 9 связаны со входами блока схем «ИЛИ» 10, выход которого соединен с кодовым входом блока деко20 дирования 11.

Управляющий выход 12 блока 11 связан с блоком управления 13, имеющим вход 14 и выход 15, и с одним из входов триггера 16, причем один выход последнего соединен с другим входом блока схем «И» 7, а другой— с другим входом блока схем «И» 9.

Управляющий выход 17 блока 11 связан со входом схемы определения кратности отказа 18, выход которой соединен с одним

30 входом схемы сравнения 19. Выход схемы 19

444250

65 связан со следующими входами: через первую дополнительную схему «И» 20, к другому входу которой подключен блок 13, со счетным входом дополнительного триггера 21, через вторую дополнительную схему «И» 22, к другому входу которой подключен выход триггера 21, со входом регистра 23 мощности корректирующего кода и непосредственно со входом регистра 24 силы корректирующего кода. Выходы регистров 23 и 24 соединсны с управляющими входамп блоков декодирования 11 и кодирования 25, кроме того, выход регистра 24 подключен к другому входу схемы 19.

Информационный выход блока 11 связан через блок схем «И» 26 с информационным выходом 27 устройства, а и;:формационный вход 28 усгройства соединен с информационным входом блока 25. Кодовый выход блока

25 связан с одним входом блока схем «ИЛИ»

29, с другим входом которого через блок схем

«И» 30 соединен инверсный выход 8 регистра

5, а выход блока схем «ИЛИ» 29 — с кодовым входом накопителя 1.

В соответствии с максимальной кратностью имеющих место в ячейках накопителя 1 отказов блоки 11 и 25 настраиваются па корректирующий код, мощность и сила которого определяются соответственно регистрами 23 и

24 путем записи в этп регистры определенных слов (под мощностью m корректирующего кода подразумевается его способность исправлять все ошибки кратностью от 1 до m включительно, а под силой и корректирующего кода подразумевается его способность обнаруживать все ошибки кратности от 1 до и включительно) . Настройка блоков 11 и 25 происходит следующим образом.

В начале работы устройства, когда отказы ь ячейках накопителя 1 отсутствуют, блоки

11 и 25 с помощью регистров 23 и 24 настроены на код, мощность которого равна О, а сила — s, где s-кратность возникающего отказа (имеющие место в яечейках накопителя 1 отказы являются результатом накопления в этих ячейках возникающих в разные моменты времени отказов кратности s, равной, например, 1). При обнаружении в какой-ниоудь ячейке накопителя 1 отказа кратности 1 блоки 11 и 25 с помощью регистров 23 и 24 настраиваются на код, мощность которого равна 1, а сила — 2; в случае обнаружения отказа кратности 2, что возможно, когда в ячейке, содержащей одиночный отказ, произойдет еще один одиночный отказ, блоки 11 и 25 настраиваются на код с той же мощностью, рав ной 1, но с силой — 3 и так далее.

В исходном состоянии триггер 16 спгналом с блока 13 устанавливается в состояпие : ».

На вход 2 подается адрес ячейки, к ко.и >0. i необходимо обратиться.

При записи информационное слово по входу

28 поступает в блок 25, с выхода которого кодовое слово через блок схем «ИЛИ» 29 записывается в накопитель 1.

При считывании кодовое слово из накопителя 1 поступает в регистр 5, "сп,рямо-о выхода б регистра 5 через блоки схем «И» 7 и

«ИЛИ» 10 — в блок 11. Блок 11 декодирует кодовое слово, определяет наличие или отсутсгвие неисправимой ошибки в нем, выдавая в соответствии с этим по управляющему выходу 12 сигнал В блок 13 и у1!равляя триггером 16, а так>ко определяет кратность ошибки (исправимой илп неисправимой), информация об этом поступает по управляющему выходу 17 в схему 18 (B качестве схемы

18 может быть использоьан накапливающий сумматор) .

В случае отсутствия неисправной ошибки триггер 16 остается в состоянии «О», Информационное слово с выхода блока 11 через блок схесм «И» 26 поступает на выход 27.

При наличие неисправимой ошибки триггер

16 сигналом с управляющего выхода 12 блока 11 устанавливается в состояние «1», подключая инверсный выход 8 регис цра 5. При этом информационное слово на выход 27 не поступает, а обратный код содержащегося в регистре 5 кодового слова с инверсного выхода 8 через блок схем «И» 30, блок схем

«ИЛИ» 29 записывается в ту же ячейку нако пителя 1. Далее производится считывание записанного в накопителе 1 кодового слова и запись его в регистр 5. Обратный код нового содержимого регистра 5 поступает с инверсного выхода 8 через блок схем «И» 9, блок схем «ИЛИ» 10 в блок 11. Блок 11 декодирует кодовое слово, выдавая через блоксхем «И»26 выход 27 п равильное информационное слово, и определяет кратность возможно имеющей место (исправимой) ошибки, информация о которой поступает по управляющему выходу

17 в схему 18 и суммируется с прежним содержанием этой схемы.

По окончании считывания, содержимое схемы 18, представляющее собой величину кратности имеющего место в ячейке накопителя 1 отказа, сравнивается схемой 19 с содержимым регистра 24.

Если схема 19 определяет равенство кратности отказа и силы используемого кода, вся информация из накопителя 1 выводится.

Затем схема 19 изменяет содержимое регистра 24, если. триггер 21 находится в состоянии

«1», то и содержимое регистра .23 (через схему «И» 22), после чего сигналом со схемы

19 через схему «И» 20 переключается триггвр

21. С помощью триггера 21, который в начале работы устройства, когда отказы в ячейках накопителя 1 отсутствовали, установлен сигналом с блока 13 в состояние «1», изменяется содержимое, регистра 23. С изменением содс ржимого регистра 24 (и регистра 23) блоки 11 и 25 перестраиваются на,код, у которого сила (и мощность) на единицу (для s=1) выше силы(и мощности) прежнего кода. После того, как перестройка блоков 11 и 25 завершена, информация в накопитель вводится.

444250

Составитель В. Рудаков

Текред М. Семенов

Редактор С. Ежкова

Корректор А. Васильева

Заказ 782/19 Изд. № 412 Тираж 591 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 7К-35, Раушская наб., д. 415

Типография, пр. Сапунова, 2

Если кратность отказа будет меньше силы используемого кода, указанные операции: вывод информации из накопителя 1, изменение содержимого регист1ра 24 и, возможно, регистра 23, и перестройка блоков 11 и 25, переключение приггера 21, ввод информации в накопитель 1 — не производится, и блоки 11 и 25 продолжают использовать прежний код.

Предмет изобретения

Запоминающее устройство с автономным контролем, содержащее накопитель, подключенный к одному блоку схем «ИЛИ» и регистру кодового слова, блоки кодирования и декодирования, подсоединенные к регистру силы корректирующего кода, схеме сравнения, схеме определения кратности отказа, блоки схемы «И», подключенные к регист1ру кодового слова, триггеру, другому блоку схем «ИЛИ» и блоху управления, отличаю щ е е с я тем, что, с целью повышения эффективной емкости устройства, оно содержит

5 дополнительные схемы «И», дополнительный триггер и регистр мощности корректирующего кода, один вход первой дополнительной схемы «И» подключен к выходу схемы сравнения, друго" — к блоку управления, а выход—

IO к одному из входов дополнительного триггера, другой вход которого подсоединен к блоку управления, а выход — к одному из входов второй дополнительной схемы «И», другой вход которой подключен к выходу схемы

15 сравнения, а выход — ко входу регистра мощности ко рректирующего кода, выход которого соединен со входами блоков кодирования и декодирования.