Многоканальная дискретно-аналоговая суммирующая линия задержки

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ ш1 444316

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 19.04.72 (21) 1774195/26-9 с присоединением заявки Ме (32) Приоритет

Опубликовано 25.09.74. Бюллетень М 35

Дата опубликования описания 03.10.75 (51) М. Кл. H 03k 5(159

Государственный комитет

Совета министров СССР (53) УДК 621.374.38 (088.8) по делам изобретений и открытий (72) Авторы изобретения

В. Я. Басин и М. А. Шевчук (71) Заявитель

Ленинградский ордена Ленина политехнический институт им. М. И. Калинина (54) МНОГОКАНАЛЬНАЯ ДИСКРЕТНО-АНАЛОГОВАЯ

СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ пульсов.

Изобретение относится к радиотехнике и может быть использовано для суммирования импульсных сигналов, запаздывающих во времени относительно друг друга.

Известна многоканальная дискретно-аналоговая суммирующая лилия задер>кки, содержащая устройства задержки, каждое из которых имеет двухтактные многоемкостные дискретно-аналоговые линии задержки, включенные через двухвходовые сумматоры последовательно друг с другом, тактовые входы которых подключены к генератору тактовых импульсов, при этом один из выходов генератора тактовых импульсов связан с распределителем импульсов, выходы которого подсоединены к управляющим входам ключей, коммутирующих запоминающие конденсаторы линий задержки.

Цель изобретения — расширение динамического диапазона многоканальной дискретноаналоговой линии задержки.

Для этого в нее введен многовходовый сумматор, входы которого подключены к выходам устройств задержки, а вторые входы двухвходовых сумматоров, входы каждого из устройств задер>кки и один из входов многовходового сумматора подключены к источникам входных сигналов.

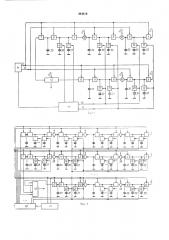

На фиг. 1 приведена функциональная схема двухканальной дискретно-аналоговой суммирующей линии задержки; на фиг. 2 — полная функциональная схема многоканальной дискретно-аналоговой суммирующей линии задержки; на фиг. 3 — диаграммы напряжений

5 в различ ых точках двухканальной дискретноаналоговой суммирующей линии задержки, Предлагаемая линия задержки состоит из

m каналов, имеющих по q ячеек в каждом канале, представляющих собой устройства

10 задержки, каждое из которых имеет двухтактпые многоемкостные дискретно-аналоговые линии задержки. Последний канал имеет на одну ячейку меньше, чем все остальные. На эти каналы подается и импульсов. Следова15 и тельно, на каждый канал подается по — имт

Для простоты рассматривается многока2О нальная дискретно-аналоговая суммирующая линия задержки, которая имеет два канала (т = 2), содержащих по две ячейки (q = 2).

Первый канал имеет на одну ячейку больше, т. е. три ячейки.

25 Число импульсов, подаваемых на такую линию задержки, равно шести (и = д . т+ m =

=2 2+2=6).

Двухканальная дискретно-аналоговая суммирующая линия задержки содержит ключи

Зо 1 — 12; ключи 13 — 22, коммутирующие конден4443I6 саторы; запоминающие конденсаторы 23 — 32, коммутируемые ключами 13 — 22; промежуточные конденсаторы 33 — 37; двухвходовые сумматоры 38 — 40; генератор тактовых импульсов 41; распределитель импульсов 42; много- 5 входовый сумматор 43; импульсы последовательностей U, и U, стробирующих ключи 1—

12; импульсы последовательностей VI u управляющих работой ключей 13 — 22; аналоговые входные сигналы 10

U„, — U„,; выборочные значения сигналов выход, выхв, на выходе входных ключей соответствующих ячеек; моменты времени 1,д,..., соответствующие моментам появления тактовых импульсов последовательности UI, моменты времени соответствующие моментам появления 20 тактовых импульсов последовательности U<.

Импульсы последовательности U> задержаны относительно импульсов последовательности U> на половину периода. 25

Линия задержки работает следующим образом.

B первый момент времени tl (см. фиг. 3) импульсом последовательности Ul открываются ключи 1,3,5,7,8, 10, 12, 30

Импульсом последовательности Vl открываются ключи 13, 15, 19, 21, коммутирующие запоминающие конденсаторы 23, 25, 29, 31.

В этот момент на выходах ключей 1, 3, 5, 8, Ç5

10 появляются (соответственно) выборочные значения сигналов

Эти напряжения запоминаются на конденса- 40 торах 23, 25, 27, 29, 31. На выходах ключей 7 и 12 напряжения нет, так как на конденсаторах 35 и 37 не было записи выборочных значений сигналов. В этот момент выборочное значение последнего сигнала U>, поступает 45 в сумматор 43.

В следующий момент t > открываются ключи 2, 9, 4, 11, 6 импульсом последовательности

U, а импульсом последовательности V открываются ключи 14, 20, 16, 22, коммутирующие 50 запоминающие конденсаторы 24, 26, 30, 32.

На этих конденсаторах не было записи сигналов, и напряжения на выходах ключей 2, 9, 4, 11 отсутствуют. На выходе ключа 6 будет напряжение U>,, считанное с запоминающего 55 конденсатора 27, которое запоминается на промежуточном конденсаторе 35.

В момент времени tq импульсом последовательности Ul открываются ключи 1, 8, 3, 10, 5, 12, 7, а импульсом последовательности V> — б0 ключи 14, 20, 16, 22, коммутирующие запоминающие конденсаторы 24, 30, 26, 32. В этот момент времени на выходе ключа 1 появляется выборочное значение сигнала U„„ которое запоминается на конденсаторе 24. 65

Аналогично па выходах ключей 8, 3, 10, 5 появляются значения U,, U,„Ó,„Ó,., которые запоминаются на конденсаторах 30, 26, 32, 27.

В этот же момент выборочное значение сигнала U,, считывается с промежуточного конденсатора 35 в сумматор 43, так как ключ 7 открыт. На конденсаторе 37 напряжение отсутствует, и на выходе ключа 12 сигнала нет.

В сумматор 43 в этот момент приходит выборочное значение сигнала U„.

Напряжение на выходе сумматора 43 будет равно U„+ U,, В момент времени 1 открываются ключи 2, 9, 4, 11, б импульсом последовательности U

zl ключи 13, 19, 15, 21 импульсом последовательности Vl. При этом подключаются запоминающие конденсаторы 23, 19, 25, 31. На выходе ключа 2 появляется напряжение U которое считано с конденсатора 23 и запоминается в этот же момент на промежуточном конденсаторе 33. На выходе ключа 9 появляется напряжение U,, которое считано с конденсатора 29 II запоминается в этот же момент на промежуточном конденсаторе 36. На выходе ключа 4 появляется напряжение U... которое считано с конденсатора 25 и запоминается на промежуточном конденсаторе 34. На выходе ключа 11 появляется напряжение Uz„считанное с конденсатора 31 и запоминающееся на промежуточном конденсаторе 37. На выходе ключа б появляется напряжение U,, считанное с конденсатора 27 и запоминающееся на промежуточном конденсаторе 35.

Далее процессы повторяются.

При этом динамический диапазон ячеек в m раз меньше, чем в прототипе, и число их в т раз меньше. Следовательно, динамический диапазон расширяется в т раз.

Предмет изобретения

Многоканальная дискретно-аналоговая суммирующая линия задержки, содержащая устройства задержки, каждое из которых имеет двухтактные многоемкостные дискретно-аналоговые линии задержки, включенные через двухвходовые сумматоры последовательно друг с другом, тактовые входы которых подключены к генератору тактовых импульсов, при этом один из выходов генератора тактовых импульсов связан с распределителем импульсов, выходы которого подсоединены к управляющим входам ключей, коммутирующих запоминающие конденсаторы линий задержки, отличающаяся тем, что, с целью расширения динамического диапазона, в нее введен многовходовый сумматор, входы которого подключены к выходам устройств задержки, а вторые входы двухвходовых сумматоров, входы каждого из устройств задержки и один из входов многовходового сумматора подключены к источникам входных сигналов

444316

С2 Г3 " 5 гв t -ч ig /tg. и Р2

080 к

U5

Йи 5

2 як s

Уаьг

S) /й к 5

Й ык 5 б

Составитель К). Еркин

Текред T. Миронова

Корректор В. Брыксина

Редактор T. Загребельная

Типография, пр. Сапунова, 2

Заказ 1721/2 Изд. № 568 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5