Быстродействующий счетчик

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1п 44433О

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 18.03.71 (21) 1636086 26-9 с присоединением заявки зче (32) Приоритет

Опубликовано 25.09.74. Бюллетень М 35

Дата опубликования описания 03.04.75 (51) М. Кл. Н 03k 23/02

Государственный комитет

Совета Чинис тров СССР по делам изобретений и открытий (53) УДК 621.374.22 (088.8) (72) Авторы изобретения

В. А. Грехнев и Б. Л. Останков (71) Заявитель (54) БЫСТРОДЕЙСТВУЮЩИЙ СЧЕТЧИК

Изобретение относится к вычислительной технике и может быть использовано для суммирования последовательности входных импульсов.

Известен быстродействующий счетчик на элементах И вЂ” НЕ, каждый разряд которого выполнен на основе Д цриггера, который содержит триггер памяти и два коммутационных триггера, причем единичный .выход тригге ра памяти соединен с единичным входом первого коммутационного триггера, у которого нулевой выход соединен с единичным входом триггера памяти, а единичный выход— с единичным входом второго коммутационного триггера, нулевой выход которого соединен с нулевым входом триггера памяти и нулевым входом первого коммутационного триггера.

Цель изобретения — уменьшение числа межразрядных связей и нагрузки íà выходы элементов И вЂ” НЕ.

Это достигается тем, что единичный выход второго коммутационного триггера каждого разряда соединен с нулевым и единичным входом первого коммутационного триггера последующего ста1ршего разряда.

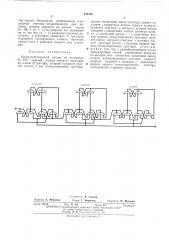

На чертеже изображена схема предлагаемого быстродействующего счетчика.

В .каждом разряде схемы И вЂ” НЕ 1 и 2 образуют триггер .памяти, И вЂ” НŠ— 3 и 4— второй коммутационный триггер, а И вЂ” НЕ 5 и 6 образуют первый коммутационный триггер. Первый разряд счетчика работает как обычный триггер со счетным, входом. Срабатывание же второго разряда возможно лишь п ри наличии сигнала, переноса на выходе схемы И вЂ” НЕ 3 первого разряда, что указывает на то, что в первом разряде записана единица. Поскольку значение сигнала на выходе схемы И вЂ” НЕ 3 не изменяется .в течение действия тактирующего сигнала, то возможность появления опасных состязаний полностью исключена. Срабатывание третьего разряда осуществляется при наличии сигнала переноса на выходе схемы И вЂ” НЕ 3 второго

15 разряда, что указывает на то, что триггер памяти второго разряда находится в состоянии

«единица» и имеется сигнал переноса с выхода схемы И вЂ” НЕ 3 первого разряда, т. е. что и триггер памяти первого разряда нахо20 дится в состоянии «единица». Весь процесс формирования сигналов суммы и переноса осуществляется схемами И вЂ” НЕ 3 и 6 до прихода тактирующего сигнала. Тактирующий сигнал осуществляет только одновременную

25 запись результатов суммирования в триггеры памяти счетчика. Таким образом, с приходом тактирующего сигнала триггер памяти третьего разряда изменит свое состояние на противоположное, а триггеры памяти перво30 го и второго разрядов установятся в состоя444330

Предмет изобретения

3 ра. ряд

2 разряд

Составитель В. Грехнев

Редактор А. Морозова Техред Т. Миронова Корректор М. Щипкова

Заказ 789/18 Изд. л1о 400 Тираж 81! Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская паб., д. 4/5

Типография, пр. Сапунова, 2 ние «нуль». Лналогично срабатывание п-oro разряда счетчика осуществляется п ри наличии сигнала переноса .на выходе схемы

И вЂ” HE 3 (n — 1)-го разряда, что указывает на то, что все (п — 1) разрядов счетчика находятся в состоянии «единица». С приходом очередного тактирующего сигнала триггеры памяти всех и разрядов изменят свое состояние.

Быстродействующий счетчик на элементах

И вЂ” НЕ, каждый разряд которого выполнен на основе Д-тригге1ра, который содержит триггер памяти и два коммутационных триггера, причем единичный выход триггера памяти соединен с единичным входом первого коммутационного триггера, у,которого нулевой выход соединен с единичным входом триггера памя5 ти, а единичный выход — с единичным входом второго коммутационного триггера, нулевой выход которого соединен с нулевым входом трпгге1ра памяти и нулевым входом первого коммутационного триггера, о т л и ч а ю10 щи и ся тем, что, с целью уменьшения числа межразрядных связей, уменьшения нагрузки на выходы этих элементов, единичный выход второго коммутационного триггера каждого разряда соединен с нулевым и единичным

15 входом первого коммутационного тригге1ра последующего старшего разряда.