Устройство синхронизации по циклам

Иллюстрации

Показать всеРеферат

п) 444336

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Ф"" а1К (61) Зависимое от авт. свидетельства (22) Заявлено 28.01.72 (21) 1742059/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 25.09.74. Бюллетень № 35

Дата опубликования описания 15.04.75 (51) М Кп H 0417/08

Государственный комитет

Совета Министров СССР по делам изобретений (53) УДК 621.394.662 (088.8) н открытий (72) Авторы изобретения

С. А. Даниэлян, М. Н. Колтунов, Г. В. Коновалов, 3. И. Лангуров и Л. Г. Михайлова (71) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ

Изобретение относится к технике приема дискретных сообщений в условиях интенсивных импульсных помех.

Известны устройства синхронизации по циклам, содержащие последовательно соединенные управляемый фазируемый делитель, реверсивный усреднитель «п» порядка, к управляющему входу которого подключен дешифратор синхрогруппы, и управляемый формирователь синхросигнала. Однако эти устройства при произвольном числе позиций в цикле обладают замедленной скоростью накопления полезного циклового сигнала и, соответственно, низкой скоростью фильтрации помехи, что снижает помехоустойчивость устройства.

Цель изобретения — повышение помехоустойчивости устройства при произво.пьном числе импульсных позиций в цикле.

Достигается поставленная цель тем, что фазируемый делитель выполнен в виде независимых делителей, первый из которых управляется тактовыми импульсами непосредственно, а второй через блок выравнивания, причем один из дополнительных выходов второго делителя соединен со входом блока изменения коэффициента деления, а другой дополнительный выход через блок изменения коэффициента деления подключен ко входу блока выравнивания и через блок начальной установки фазы — к цепи сброса первого делителя.

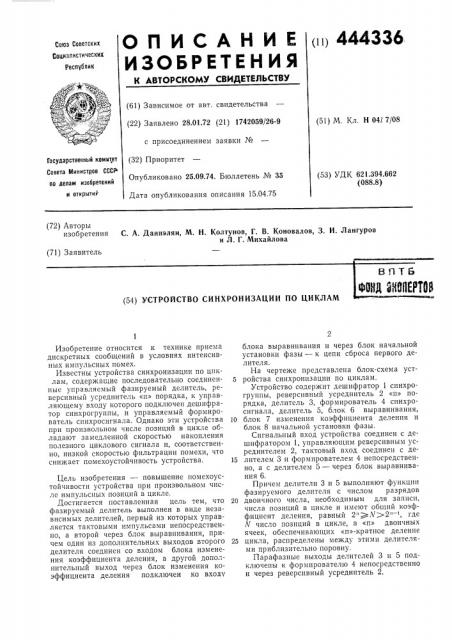

На чертеже представлена блок-схема уст5 ройства синхронизации по циклам.

Устройство содержит дешифратор 1 синхрогруппы, реверсивный усреднитель 2 «и» порядка, делитель 3, формирователь 4 синхросигнала, делитель 5, блок 6 выравнивания, 10 блок 7 изменения коэффициента деления и блок 8 начальной установки фазы.

Сигнальный вход устройства соединен с дешифратором 1, управляющим реверсивным усреднителем 2, тактовый вход соединен с де15 лителем 3 и формирователем 4 непосредственно, а с делителем 5 — через б.пок выравнивания 6.

Причем делители 3 и 5 выполняют функции фазируемого делителя с числом разрядов

20 двоичного числа, необходимым д.пя записи, числа позиций в цикле и имеют общий коэффициент деления, равный 2" ) V) 2"- где

N число позиций в цикле, а «п» двоичных ячеек, обеспечивающих «п»-кратное деление

25 цикла, распределены между этими делителями приблизительно поровну.

Парафазные выходы делителей 3 и 5 подключены к формирователю 4 непосредственно и через реверсивный усреднитель 2, 444336

Выравнивание числа тактовых интервалов в делителе 5 производится с помощью блока

6 выравнивания, управляемого блоком 7 изменения, входы которого соединены с дополнительными выходами делителя 5.

Выравнивание числа тактовых интервалов в делителе 3 обеспечивается изменением начальной фазы деления один раз за половину цикла, для чего один из дополнительных выходов делителя 5 подключен через блок 8 начальной установки фазы к цепи сброса делителя 3.

Устройство работает следующим образом.

При подаче тактовых импульсов в течение первой половины цикла делитель 3 распределяет позиции цикла поровну между выходами делителя (k — 1) способом. Если число позиций в цикле не кратно 2 —, то в следующем подцикле начальная фаза делителя 3 устанавливается с выхода делителя 5 таким образом, что на те выходы, на которые в течение первого подцикла попало меньше тактовых интервалов в этот подцикл, поступает дополнительное число тактовых интервалов и наоборот. В результате (k — 1) накопителей в реверсивном усреднителе 2 работает с максимально возможной достоверностью. Остальные п — 1+1 накопителей получают сигналы с делителя 5, имеющих равнине число тактов на каждом выходе за счет того, что с блока 6 выравнивания поступают сигналы на делитель 5 через разные промежутки времени, подбираемые с помощью блока 7 изменения таким образом, что при изменении фазы делителя 5 изменяется коэффициент деления выравнивателя 6. Коэф5 фициент выравнивателя 6 подбирается, исходя из соотношений, между N и 2" — "+ и изменяется на +- 1 или не изменяется, сохраняя при этом 2" — +1 степеней симметрии.

Предмет изобретения

Устройство синхронизации по циклам, содержащее последовательно соединенные управляемый фазируемый делитель, реверсивный усреднитель «п» порядка, к управляюще15 му входу которого подключен дешифратор синхрогруппы, и управляемый формирователь синхросигнала, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости устройства при произвольном числе импульсных

20 позиций в цикле, фазируемый делитель выполнен в виде двух независимых делителей, первый из которых управляется тактовыми импульсами непосредственно, а второй — через блок выравнивания, причем один из дополни25 тельных выходов второго делителя соединен со входом блока изменения коэффициента деления, а другой дополнительный выход через блок изменения коэффициента деления подключен ко входу блока выравнивания и через

30 блок начальной установки фазы — к цепи сброса первого делителя.

444336

7актИвi

Cuz

Составитель В Евдокимова

Техред Т. Курилко

Редактор А. Морозова

Корректор О Тюрина

Типография, пр. Сапунова, 2

Заказ 895/15 Изд. № 415 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, K-35, Раушская наб., д. 4/5