Преобразователь частотно-импульсных сигналов в цифровой код

Иллюстрации

Показать всеРеферат

эвьтс н 1»

Ф, .> .:

О П И С А Н И Е (11) 445I48

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических енеспублии

К АВТОРСКОМУ СВИДЯТВЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) Заявлено 28.09й72 (21Х831898/26-9 (51) М Кл. с присоединением заявниН 03к I3/20 т ссуде рстеенный комитет

Совете Министров СССР оо делам изобретений и открытий (32) Приоритет—

Опубликовано 30. 09.7 Бюллетень № . 36 (45)! Дата опубликования описанитй.О. О.Я. (53) УЙК, 68I .325 (088.8) (72) Авторы изобретения

Г.О. Паламарюк и А.К. Костенич

Рязанский радиотехнический институт (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТНО- ИМПУЛЬСНЫХ

СИГНАЛОВ В ЦИФРОВОЙ КОД

Изобретение относится к области вычислительной и измерительной техники.

Известен преобразователь частотно-импульсных сигналов в код, содержащий генератор эталонной час тоты, делители частоты, схемы переноса кода, инвертор, схемы совпадения, схемы сборки, схему выделения разности периодов, выходы 1о которо подключены к шийам сложения и вычитания реверсивного счетчика, а выходы разрядов последнего соедйнены с входами двоичного умножителя, другие входы которого 15 подключейы к выходу первого делителя частоты.

Однако известныИ преобразователь характеризуется большим временем переходного процесса при положительном приращении входной частоты и значительной пульсациеИ кода реверсивного счетчика, вызванноР неравномерной расстановкоИ последовательности импульсов, заполняющих разность периодов.

Цель изобретения - повышение

2 точности и увеличение быстродействия преобразователя. для этого в предлагаемом преобразователе выход двоичного умножителя подключен к входу первой схемы совпадения, которая другим входом соединена с выходом инвертора и выходом через первую схему сборки — с входом второго делителя частоты, другой вход первой схемы сборки подключен к выходу второй схемы совпадения, которая одним входом подключена к выходу генератора эталонноИ частоты и другим - к входу инвертора, шине сложения реверсивного счетчика и первому входу третьей схемы совпа-дения, выходом соединенной с первыми входами второИ и третьеИ схем сборки и вторым входом — с выходом первого делителя частоты и входом четвертоИ схемы совпадения, которая вторым входом соединена с выходом инвертора и выходом — с входом третьего делителя частоты, вход второИ схемы сборни соединен с входом инвертора, а выход ее—

445ИЗ

5 с импульсным входом первой схемы переноса кода, выход третьей схемы сборки подключен к импульсно му входу реверсивного счетчика, а второй ее вход подключен к им- пульсному входу второй схемы пере носа кода и выходу пятой схемы совпадения, которая одним вхолом соединена с шиной вычитания реверсивного счетчика и другим входом — 0 с выходом второго делителя, частоты, входы разрядов которого подключейы к выходам второй схемы переноса кода, входы которой подключены к выходам разрядов третьего де- 15 лителя частоты и входам первой, схемы переноса кода, которая выходами подключена к входам разрядов первого делителя частоты.

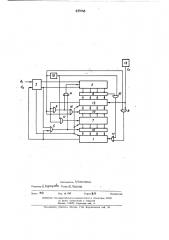

Па чертеже представлена схема предлагаемого преобразователя.

Преобразователь работает следующим образом.

При отрицательном приращении входной частоты ($ â€, ) к 25 импульс переполнения управляемого делителя частоты I, имеющего коэффициент деления 2 ", поступает на схему 2 выделения разности периодов раньше им ульса входной частсты (, с. ), и схема вы деления разностй периодов формирует строб длительностью

Ж -с. Ь. где . . 4 . — частота, соответствУюЩаЯ значению коДа A о 4о реверсивного счетчика 3 в предыдущем периоде.

Тогда на время Л (к вычитающему входу реверсивного счетчика Ы подключается через схему сбор 45 ки + и схему совпадения 5 выход правляемого делителя частоты . ак как частотная последовательность на выходе управляемого делителя частоты -1 в этом случае равна 5о частоте (F ) с выхода дво уу ичного умножителя 6, деленная на код делителя частоты 7, который пропорционален ткущему вре- 55

,т, F. (i1) а Гх(, л" ) : то можно за исать следующее уравнение 4/

Л=М вЂ” — 4 „

g I и

Код реверсивного счетчика к моменту прихода импульса частоты (т- ) ф= (х — 4 ) При положительном приращении вхсднсЙ частсты (х а . 1 имаунвс этой частоты поступает на схему 2 выделения разности периодов раньше импульса с управляемого делителя частоты 1, в котором к этому момен ту временй еще не списано число

Сформированййй схемой выделения разности периодов строб разрешает прохождение импульсов на суммирующий вход реверсивного счетчика 3, открывает схемы совпадения 8 и 9 закрывает схемы совпадения IO u iI.

Импульс, сформированный от перепада напряжения на шине сложения реверсивного счетчика, переносит код делителя частоты 7, равный

/р ./, в делитель частбты 12, и на его выход

Сунет частота, равнанди(/ j)

Разрешающий строб по ш не сло жения оканчивается в момент переполнения управляемого делителя частоты 4 и равен .Р 1 иУ

3а это время на вход реверсивного счетчика 3 поступает число импульсов д ут = втф(3 " ))- j, что соответствует числу, которое необходимо добавить к величине кода реверсивного счетчика.

° При таком способе коррекции (при положительном приращении входной частоты) максимальная величина разности периодов д7 определяется из выражения — да Н4ас — Ф . р У что соответствует йериоду максимальной входной частоты.

На чертеже введены также сле дующие обозначения: IS — генератор эталонной частоты I4 и 1)— схемы переноса кода; 7б и 17— схемы сборки; IH — йнвертор.

Предмет изобретения

Преобразователь частотно-импульсных сигналов в оцифровал код, содержащиИ генератор зталонной частоты, делители частоты, схемы переноса кода, инвертор, схемы совпадения и схемы сборки, схему выделения разности периодов, выходы которой подключены к шйнам, сложения и вычитания реверсивного счетчика, а выходы разрядов последнего соединены с входами двоич. ного умножителя, другие входы которого подключейы к выходу первого делителя частоты, о т л и ч а ю щ и И с я тем, что, с целью повышения точности и увеличения быстродействия преобразователя, в нем выход двоичного умножителя подключен к входу первоИ схемы совпадения, которая другим входом соединена с выходом инвертора и выходом через первую схему сборки — с входом второго делителя частоты, другоИ вход первоИ схемы сборки подключен к выходу второй схемы совпадения, которая одним входом подключена к выходу генератора зталонной частоты и другим— к входу инвертора, шине сложения

>о

М

6 реверсивного счетчика и первому входу третьей схемы совпадения, выходом соединенноИ с первыми входами второй и третьеИ схем сборки и вторым входом — с выходом первого делителя частоты и входом четвертой схемы совпадения, которая вторым входом соединена с выходом инвертора и выходом — с входом третьего делителя частоты, вход второИ схемы сборки соединен с входом инвертора, а выход ее — с импульсным входом первой схемы переноса кода, выход третьеИ схемы сборки подключен к импульсному входу реверсивного счетчика, а второй ее вход подключен к имйульсному входу второМ схемы переноса кода и выходу пятой схемы совпадения, которая одним входом соединена с шиноИ вычитания реверсивного счетчика и другим входом — с выходом второго делителя частоты, входы разрядов которого подключены к выходам второй схемы переноса кода, входы которой подключены к выходам разрядов третьего делителя частоты и входам первой схемы переноса кода, которая выходами подключена к входам разрядов первого делителя частоты.

Составитель А KOCrneHue

Редактор Е KQpQ®< Техред E ПЕтрОЬа

Закаэ

Изд, М 06 Тираж Д1 Подписное

ЦНИИПИ осударственного комитета Сове|а Министров СССР ло делам изобретений и открытий

Москва, П3035, Раушская иаб., 4

Поедприятие «Патент», Москва, Г.59, Бережковская наб., 24