Делитель импульсов

Иллюстрации

Показать всеРеферат

(ii) 44И62

ОП ИСАН И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕйЬСТВУ

Cmes Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 21.07.72 (21) 1818839/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 30.09.74. Бюллетень № 36

Дата опубликования описания 28.03.75 (51) М. Кл. Н 03k 23, 04

Государственный комитет

Совета Министров СССР (53) УДК 621.373.431.2 (088.8) по делам изооретвиий и открытий (72) Авторы изобретения, К. В. Гладков, В. А. Ермолаев и P. Б. Мурадов (71) Заявитель (54) ДЕЛИТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к области измерительной и вычислительной техники и может использоваться в различной аппаратуре.

Известен делитель импульсов, содержащий десятичный счетчик с входом установки нулевого положения, к выходам которого через дешифратор подключен коммутатор с двумя выходами, соответствующими целому и половинному коэффициентам деления. Этот делитель имеет низкую точность деления импульсов.

Цель изобретения — повышение точности деления имгульсов.

Для этого в делитель имгульсов дополнительно включены элемент «ИЛИ» с двумя входамп, элемент «И» и триггер с раздельными входами, один из которых соединен непосредственно с выходом коммутатора целого коэффициента деления, входом установки нулевого положения десятичного счетчика и с одним из входов элемента «ИЛИ», а другой вход триггера соединен с выходом коммутатора половинного коэффициента деления, причем выход триггера с раздельными входами через элемент «И» соединен с другим входом элемента «ИЛИ».

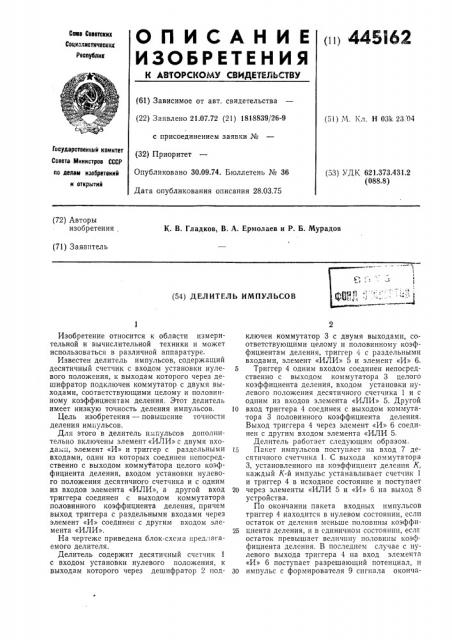

На чертеже приведена блок-схема предлагаемого делителя.

Делитель содержит десятичный счетчик 1 с входом установки нулевого положения, к выходам которого через дешифратор 2 подключен коммутатор 3 с двумя выходами, соответствующими целому и половинному коэффициентам деления, триггер 4 с раздельными входами, элемент «ИЛИ» 5 и элемент «И» 6.

5 Триггер 4 одним входом соединен непосредственно с выходом коммутатора 3 целого коэффициента деления, входом установки нулевого положения десятичного счетчика 1 и с одним из входов элемента «ИЛИ» 5. Другой

10 вход триггера 4 соединен с выходом коммутатора 3 половинного коэффициента деления.

Выход триггера 4 через элемент «И» 6 соединен с другим входом элемента «ИЛИ 5.

Делитель работает следующим образом, 15 Пакет импульсов поступает на вход 7 десятичного счетчика 1. С выхода коммутатора

3, установленного на коэффициент деления К, каждый К-й импульс устанавливает счетчик 1 и триггер 4 в исходное состояние и поступает

20 через элементы «ИЛИ 5 и «И» 6 на выход 8 устройства.

По окончании пакета входных импульсов триггер 4 находится в нулевом состоянии, если остаток от деления меньше половины коэффи25 циента деления, и в единичном состоянии, если остаток превышает величину половины коэффициента деления. Б последнем случае с нулевого выхода триггера 4 на вход элемента

«И» 6 поступает разрешающий потенциал, и

30 импульс с формирователя 9 сигнала оконча445162

Предмет изобретения

Составитель Ю. Еркин

Техред T. Миронова

Редактор Е. Караулова

Корректор Л. Денисова

Заказ б89/14 Изд. М 1108 Тираж 811 Подписное

UHHHHH Государственного комитета Совета Мишьстров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ния пакета входных импульсов поступает на выход 8 устройства через элементы «ИЛИ»

5 и «И»6.

Делитель импульсов, содержащий десятичный счетчик с входом установки нулевого положения, к выходам которого через дешифратор подключенк коммутатор с двумя выходами, соответствующими целому и половинному коэффициентам деления, отличающийся тем, что, с целью повыщения точности деления, в него дополнительно включены элемент «ИЛИ» с двумя входами, элемент «И» у триггер с раздельными входами, один из которых соединен непосредствен5 но с выходом коммутатора целого коэффициента деления, входом установки нулевого положения десятичного счетчика и с одним из входов элемента «ИЛИ», а другой вход триггера соединен с выходом коммутатора поло10 винного коэффициента деления, причем выход триггера с раздельными входами через элемент «И» соединен с другим входом элемента «ИЛИ.