Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСА НИ Е

ИЗОБРЕТЕН ИЯ

) М6052

Союз Советских

Социалистииеслих

Реслублик

/ к автовскомю свидатальствю (61) Зависимое от авт. свидетельства— (22) Заявлено 05,0Х е73 (21,) 876745/XS-2 (51) М Кп. с присоединением заявки—

Я- Оба 5/00

Госудврстввииый комитет

Совете Мииистров СССР оо долом изобретений и откритий (32) ПриоритетовЂ

Опубликовано0510о7 Втоллетеиь Re (бз) ь дк 68Х.527. .6 (088о8) (45уДата опубликования описания 75 ° 10 ° 7 (72) Авторы изобретения

А.В. Тимашев и А.В. Иванов

Особое конструкторское бюро вычислительной техники

Рязанского радиотехнического института (Л) Заявитель

/ (s4) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЗСТВО

Изобретение относится к области автоматики и вычислительной технике и может быть использовано в импульсных и цифровых устройствах. 5

Известны буферные запоминающие устройства, предназначенные для снижения до допустимого зна. чения местной (по времени) частоты

: следования импульсов и содержа- 1о щие двоичный счетчик, ячейку памяти и узел управления.

Однако быстродействие таких устройств ограничено из-за невозможности одновременного действия 15 на счетчик последовательности входных импульсов и импульсов, поступающих с выхода узла управления.

К недостаткам известных устройств относится также необходимость жес- ) твой синхронизации моментов времени воздействия входной и выход-. ной частот, приводящая к логичес- кой сложности управляющих этими частотами схем.

ПРедлагаемое уствойство от-.

2 личается тем, что в нем шина вы ходных импульсов и шина входны, импульсов подключены ко входам первой, схемы "И" и через элементы задержки к первым нходам соответственно второй и третьей схем "И".

Выход первой схемы "И" через схе формирования сигнала запрета соединен со вторыми входами второй и третьей схем "И". Выход второй схему "И" подключей к суммирующему входу двоичного счетчика, а выход третьей схемы "И" zo входу узла управления.

Это позволяет повысить быстродействие устрою™ тва.

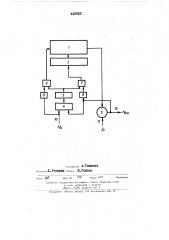

Схема буферного запоминающего устройства показанлна чертеже устройство содержит л -pasрядный двоичный счетчик I, узел управления 2, элемент памяти 3, первую схему™И" 4, схему формйрования сигнала запрета 5, вторую схему "И" 6, третью схему "И" 7, элементы задержки 8 и 9, шицу вход— aalu импульсов IO, шину опроса П и

5 о 5

25

45

3 шину выходных импульсов I2. устройство работает следующим образом.

Входные импульсы текущей частоты fg, поступают на первый вход первой схемы " 4 и через элемент задержки 8 на первый вход второй схемы "И" 6. При прохождении входного импульса через схем и а содержжюе счетчика I увеличивается на единицу. Импульс опрашивающей частоты, в случае, если в ячейке памяти 3 записана единица, вызывает появление выходного импульса. Одновременно выходной импульс поступает на вход схемы "И"

4 и через эле;лент задержки 9 на первый вход схемы "И" 7. При прохождении выходного импульса через схему "И" 7, с помощью узла управления 2 содержимое счетчика 1 уменьшается на единицу. Наличие совместного действия входных импульсов и импульсов опрашивающей частоты с длительностями определяется схемой "И" 4. В случае несовпадения импульсов входной и выходной частот на выходе схемы

"И" 4 сигнал отсутствует, и схема форяирования сигнала запрета 5 раз решает прохождение сигналов на сум мируюврй вход счетчика I и на вход узла управления 2.

В случае если взводные импульсы и выходные импульсы перекрывают ся во времени, на выходе схемы "И"

4 возникает сйгнал с длительностью Г,, зависящей от времени совпадения этих импульсов. Схема формщ,ования сигнала запрета 5 вырабатывает сигнал запрета длительностью Я.Т, если на ее входе действует сигнал длительности а, Х . При Г (. . с ема 5 сиг нала запрета не вырабатывается m перекрывающиеся на это время сигна. лы входной и выходной частот дейст вуют на счетчик I. Однако счетчик построен таким образом, что совместное действие сигналов входной и выходной частот в течение времениГ =И не вызывает нарушения его работоспособности. Это легко осущестнить например длн счетников, реагирующих на щронт входннх импульсов и имеющих време восстановления б — — p.J.

Таким образом, если схема вырабатывает сигнал запрета, это означает, что на вход устройства действует импульс записи и одновременно подается импульс опрашивающей частоты. В этом случае состояние счетчика не меняется, так как вторая- и третья схемы "И" не пропускают эти импульсы. Если сигнал запрета отсутствует, это означает, что сигналы записи и считывания следуют неодновременно или, что время совпадения этих сигналов меньше

ПРИМЕТ ИЗОБРЕТЕНИЯ

Буферное запоминающее устройство, содержащее двоичный счетчик, выход которого через элемент памяти соединен с шиной выходных импульсов, шину входных импульсов, шину опроса, соединенную с другйм входом элемента памяти, узел управления, выход которого связан с вычитающим входом счетчика, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, шина входных импульсов и шина выходных импульсов подключе-, ны ко входам первой схемы "И" и через элемент задержки к первым входам соответственно второй и третьеи схем "И", выход первой схемы

"И" через схему формирования сигнала запрета соединен со вторыми входами второй и третьей схем "И" выход второи схемы "И" подключен к суммирующему входу двоичного счетчика, а выход третьей схемы

"И" - ко входу узла управления.

446052

44х.

Составитель Ае ТИМЯШВВ

Ретак ор Л УТОХИЕИ тек! д К,(ящщщ!!

Изд. М 1 ира;к Ф

Подписное

Закан 4У

1!!иднриятие «Патаки», Москва, (-59, Бсрс кковская наб., 24

ill!1 ill l Ill I oñóäàðñTâåïèîã0 комитета Соцста Министров СССР но делам изобретений и открытий

Москва, 1!3035, Раушская иаб., 4