Преобразователь -разрядного двоичного кода

Иллюстрации

Показать всеРеферат

всасоюзнля

ПАТЕНТ1!О-; I..Ð-.ИАЯ библиотека МБА

Союз Советских

Социалистимеских

Республик (и) 44605 З

К АВТОРСКОМУ СВИДВТВЛЬСТВУ (61) Зависимое от, авт. свидетельства— (22) Заявлеио06еОФеЯ (2@6МЗФХ/ХМ@ (51) М Кл.

g 06/ а/OO (53) УИК68Хе325е с присоединением заявки—

Гасударственный иамитет

Саввтв Министрав СССР па делам изааретений и аткрытий (32) Приоритет—

Опубликовано 05,70,74iтоллeтень № 37 (45)сДата опубликования описания 15, 0,7 .53 (088а8) В.В. Александрова Р.и. Полонникоза Т.Л. Пеинзь и В.И Степанов (72) Авторы изобретения (71) Заявитель (54) . ПРЕОБРАЗОВАТЕЛЬ l4-РИРЯДН01 О Д80ит нО О

K0Q

Изобретение относится к об- ласти автоматики и ВЫЧИСЛитеЛЬной

Т8хНМЕЕ и МохеТ быть использовано. в устройствах для обработки сигнаЛОва РаСПОЗнаваниЯ ОбРаЗЦОВ И Д 4 звестное устройство для преобразования сигналов, Выполненное в виде матрицы ттт элементов и обеспечивающее инвариантность к циклическим сдвигам сигнала Hs входе, реализует быстрое преобразованйе Фурье, но при этом элементы устройства должны вычислять модуль суммы. и модуль разности, IKTo ведет к усложнению устройства.

Цель изобретения состоит в создании болев простого устройства способного выполнять те же функции с сигналами, заданности двоичным

КОДОМ, Предложенное устройство выпол неко в виде матрицы д хт 4ункцио нальных ячеек,. где rn = t ê".

Выходы каждой i = 0 иф«)= яче1 ек g -го столбца матрицы (R 07 +

) «соединены со.щодами (2i -Х)2 и и 2 -й ячеек (Я+1)-го столбца и отличается тем, что нечетные ячейки каждого столб® матрицы выполнены на схемах "И-Не", а четныв б ячейки - на схемах неравнозначности

Это позволяет упростить устройствоо.

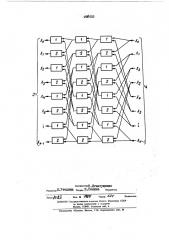

Схема устройства изображена на чертеже.

1О устройство содержит матрицу функциональных ячеек.

Столбцы матрицы Выполнены на схемах "И-НЕ" I и неравнозначнооти

2. Значение разрядов д =раз ого двоичного кода Х, Х,, Хл у ) подаются на входы 3,У вй-! ходных сигналов сншаются с Выход(и 4, Входной < -разрядный двоичный код, последовательно проходя через каждый из ж столбцов схем "-И-НЕ"

I и неравнозначности 2, приобретаЕТ СВОЙСТВО атНВаРИЙНТНОСТИ ПО Отношению к следующим операциям над разрядами Х g ° Х g y Х а ° е е ° y Ху (щ ЗхОлйх 3:

446053 ца. вновь полученная матрица чисел дает окончательный результат.

3 а) к цикличвскйм перестановкам разрядов типа

ТУ(Хр Xf Xz" XL" ХиВ) ТУ(Хлои" Мл4Й

Xgs pr-g гдв < — любое целое число, Xz>g X б) к отражениям разрядов, когда Хг образуется в Ху-i-1.Е=О.<-<

При получении таких же apeodpaзован и для сигналов, снятых с матричного рецепторного поля размером

ЮхУ двоичных сигналов, поступают следующим образом.

Осуществляют указанное преобразование для каждого as л столбцов двоичных сигналов пола и- запоминают его результаты в ниде матри-. цы чисел (размер матрицы i» ), Затем осуществляют указанное преоб. разование над строками этой матриПреобразователь hl-раз оro двоичного кода, соде матрицу ® .,функциональных ячеек, " т,де =.ИЬ", выходы каждой 1 -а ,и ()-й ячеек Я -ro столбца мат цы (=@,I, .... m) совнены со входами (2i -О-ой и

i. -ой ячеек (<+ I)-го столбца, "отличающийся тем, что, с целью упрощения устройства, нечетные ячейки казддого столбца трицы выполнены на схемах "И-ЯЕ".

® .а четные ячейки - на схемах нерав, нозначности.

СостввнтельВ,Яуцууущ щц)

Редактор Е еУТВХИНЬ Техред Н CSHHHR Корректор

Заказ фЯЯ ., Изд. М М® Тираж з ® Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 3ИОЭ5, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24