Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

Jr)

Г 1Ь, ввтент .;, Союз Советских

Социалистических

Республик (") М6(Ы (61) Зависимое от авт. свидетельства— (22) Заявлено I3.ОЕ.Я (»)XSOVVSXPeZ (51) М. Кл. с присоединением заявки

Государотвеннь и комитет

Совета Министров СССР по делам изооретений н открытий (32) Приоритет

Оттубликованф,Щ,,бюллетень № Я

Дата опубликования описаиия уД(),Дф (53) УДК

681.325.66 (888.8) (72) A в то р ы изобретения

М.k. Дуда, B.И. Дсибрсзский и Я.В. Бучниский (71) Заявитель (54) УСТРО1 СТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к устройствам вычислительной техники, в частности к цифровым системам контроля и обработки информации.

Известны устройства для с в- нения следующих друг за другом чисел, заданных последовательностью импульсов, содержащие два счетных регистра с суммирующими и вычитаю-,„ щими счетными входами, линии задер жки, инвестор и логические схемы иИН ищущий

Р

В

В этих устройствах вход регистра с суммирующим входом соеди- „ нен со входом устройства через схе" му "И", второй вход которой связан через схему "НЕ" с выходом схемы

"ипи, а вход регистра с вычитающим Входом соединен Go вхОдом vGT- 2„ ройства через схему "И", второй вход которой связан с выходом схемы "ИЛИ", входы которой в свою очередь связаны с выходами разрядов регистра с вычитающим входом, а ВХОДЫ ЭТИХ РаЗРЯДОВ СОЕДИНЕНЫ С выходами соответствующих разрядов регистра с G рующим входом через схемы ", вторые входи которых через линйю задержки соединены со входом сигнала сброса регистра с вычитающим Входом, Наиболее существенным недостатком этих устройств является большое количество регистров, а соот ветственно и малан надежность,так как для получения наибольшего или

Наименьшего из следующих друг за другом чисел необходимо два отдельных устройства, выполняющих соответственные функции.

Целью изобретения является

УСтРаНЕНИЕ ВЫШЕУКаэаННОГО НЕДОСттат ка. Для этого в предлагаемом устройстве первые входы третьего m четвертого элементов "И" подключены к первому управляющему входу устройства, втОрой управляющий вход которого соединен с пятым зле

TIPFgfПТ ИЗОБРЕТЕНИЯ

3 ментом "N" при ятом вторые взводы элементов "И", подключены к информационному входу устройства, третьи входы четвертого и пятого элементов "И" соединены с соответств выходами первого элемента

", третий вход третьего элемента "И" подключен к инверсному выходу триггера, вход которого соединен со входом первого элемента задержки, при ятом выходы третьего четвертого и пятого элементов "И" через второй элемент

"ИЛИ" подключены ко входу сложения второго регистра.

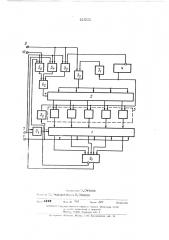

Сущность изобретения поясняет ся чертежом. устройство для сравнения двоичных чисел содержит регистр I c вычитающим и регистр 2 с суммирующим счетным входами, линии задержки 3 триггер 4, логические схемы

"И" 5,-5,и "ИЛИ" б,р входы устройства -IO.

Устройство работает следующим образом.

В йсходном состоянии регистры

I, 2 "свободны" и триггер 4 в нулевом состоянии. Если разрешающий потенциал на втором управляющем входе IO выборки наибольшего из следующих друг за другом чисел, то первое число, поступающее на ий орм рмационный вход 7 через схемы

И" 5 и "ИЛИ" 6, запи.ывается в регистр 2. Импульс сброса, поступающий после числа на вход 8, переписывает содержимое регистра 2 в регистр I и устанавливает триггер 4 в единичное состояние.

Импульсы, соответств е сле дующему числу, поступают через схему И" 5 на вычитающий вход регистра I и уменьшают его содержимое.

Если это число окажется больше записываемого в регистрах, то в тот момент, когда в разрядах регистра I будут нули, прекращается поступление импульсов очередности числа на вход регистра I и остальные импульсы числа, соответствующие разности сравнйваещл двоичных чисел, поступают на суммирующий вход регистра 2, увеличивая

его содержимое. Еслй второе число меньше первого или равно ему, то содержимое регистра 2 не изменится

Поступающий после очередного числа сигнал сброс стирает содержимое регистра Е и перезаписывает в этот регистр двоичное число, записанное в регистре 2, которое является

1 реяультатом сравнения.

При поступлении йа информацио нный вход устройства 7 следующего сравниваемого числа операция срав нения производится аналогично и результат сравнения всегда оказыва ется записанным в регистре .Е.

В случае, если разрешающий-по. тенциал на первом управляющем входе 9 выборки наименьшего из следую. щих друг за другом чисел, то первое число, поступающее на информационный вход 7 через схемы " " 5 и "ИЛИ" 6 записывается в регистр п,2. Импульс сброса, поступающий пос+ ле числа на вход 0, переписывает содержимое регистра 2 в регистр I и устанавливает триггер 4 в единичное состояние и регистр 2 в нулевое.

Ймпульсы, соответствующие следующему двоичйому числу поступают на входы регистров I и 2 через схемы "И" 5 и "И" 5, "ИЛИ" бр соответственно. В случае, если поступающее число равно или больше записанного в регистр I, то в тот момент когда в разрядах регистра I будут нули, прекращается поступление импульсов очередности числа на входы регистров I и 2. Поступающий после очередного числа сигнал сброса стирает содержимое регистра I и перезаписывает в ятот регистр двоичное

" ;число, записанное в регистре 2, ко торое является результатом сравнения, и стирает содержимое регистра

2.

В результате в регистр I будет записано наименьшее из следующих друг за другом чисел.

Устройство для сравнения двоичных чисел, содержащее элементы

"И", "ИЛИ", триггер, первый регистр, вход вычитания которого coea i динен с вы одом первого элемента

"И", первый вход которого подключен к ий4ормационному входу устройства, а вто вход — к первому выходу первого элемента "ИЛИ", входы ком торого соединены соответственно с разрядными выходами первого регистра, установочные входы которого соедйнены с выходами соответствующих алементов "И", первые входы которых подключенй соответственно к разрядным выходам второго регистра, а вторые входы — ко входу первого элемента задержки и к выходу

44 второго элемента задержки, вход которого соединен со входом сброса устройства, выход первого элемента задержки соединен с первым входом второго элемента "И", соединенного со входами установки второго регистра, при этом второй вход второго элемента "И" подключен к первому управляющему входу устройства, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства, первье входы третьего и четвертого алементов "И" подключены к первому управляющему входу устройства, второй управляющдй вход которого соединен

6 с пятым алементом "И", три ятом вторые входы элементов "И", подклю чены к информационному входу устройства, третьи входы четвертого и

5 пятого элементов "И" соединены с соответствующими выходами первого элемента "ИЛИ" третий вход третье го алемента "И" подключен к инверс ному выходу триггера, вход которою ro соединен со входом первого але-. мента задержки, при атом выходы третьего четвертого и пятого элементов "И" через второй алемент

"ИЛИ" подключены ко входу сложения

15 второго регистра.

Состанитель СЙЧИНс!! еи»к>ор 3. >PJIL7TI".ядехрел П, СЕНИНО

За>,а.i 8<+

Ти ра >и 6А4

Подписное

I l! .i>..! ии> и> «)!атеи г>, Москиа, Г >9, !>ере>кковская иаб., 24

I LI !! !! 1! 1! I осуи > рс > венного коыитеаи Соаета Министров С(Х!>

II, д>лам иаобретеиий и открьпий

Моск»а, II>035, !>аушскаи иаб., 4